# Le interconnessioni tra i dispositivi

Prof. Alberto Borghese Dipartimento di Scienze dell'Informazione

borghese@dsi.unimi.it

Università degli Studi di Milano

Riferimento Patterson: 6.1-6.3

A.A. 2009-2010

1/38

$http: \hspace{-0.05cm} \hspace{-$

### **Sommario**

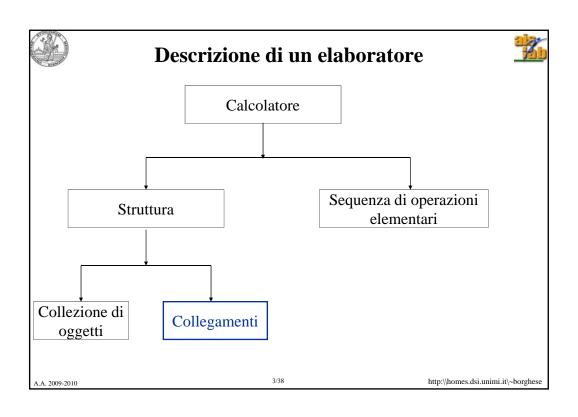

#### Le interconnessioni

La gestione delle interconnessioni

La gestione dell'I/O

A.A. 2009-2010

2/38

# Dispositivi di I/O - classificazione

| Device               | Behavior        | Partner | Data rate (Mbit/sec) |

|----------------------|-----------------|---------|----------------------|

| Keyboard             | Input           | Human   | 0.0001               |

| Mouse                | Input           | Human   | 0.0038               |

| Voice input          | Input           | Human   | 0.2640               |

| Sound input          | Input           | Machine | 3.0000               |

| Scanner              | Input           | Human   | 3.2000               |

| Voice output         | Output          | Human   | 0.2640               |

| Sound output         | Output          | Human   | 8.0000               |

| Laser printer        | Output          | Human   | 3.2000               |

| Graphics display     | Output          | Human   | 800.0000-8000.0000   |

| Cable modem          | Input or output | Machine | 0.1280-6.0000        |

| Network/LAN          | Input or output | Machine | 100.0000-10000.0000  |

| Network/wireless LAN | Input or output | Machine | 11.0000-54.0000      |

| Optical disk         | Storage         | Machine | 80.0000-220.0000     |

| Magnetic tape        | Storage         | Machine | 5.0000-120.0000      |

| Flash memory         | Storage         | Machine | 32.0000-200.0000     |

| Magnetic disk        | Storage         | Machine | 800.0000-3000.0000   |

A.A. 2009-2010

5/38

$http: \hspace{-0.05cm} \hspace{-$

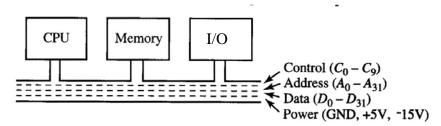

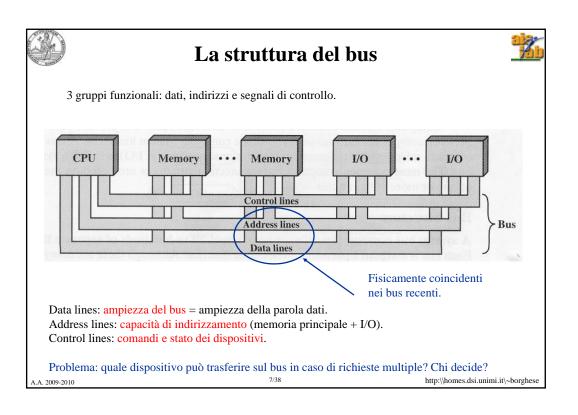

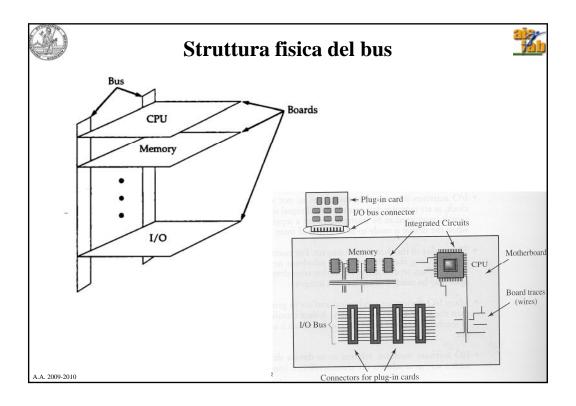

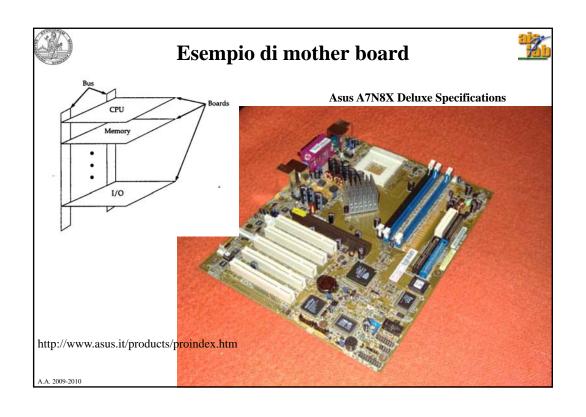

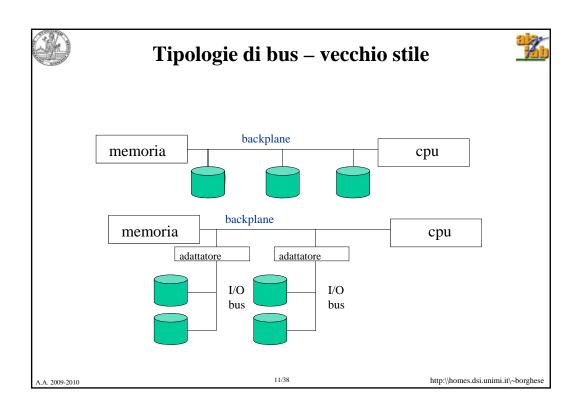

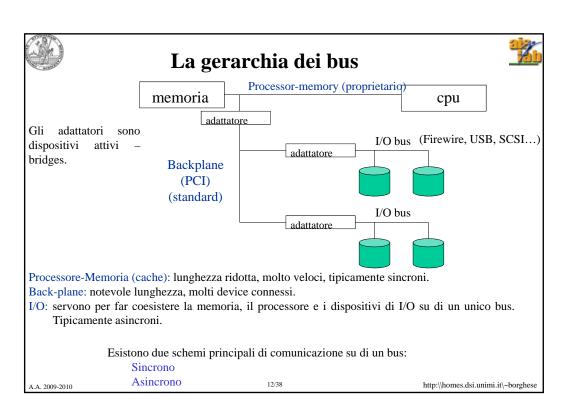

# Il bus (connessione a cammino comune)

Pathway che connette tutti i dispositivi in modo bidirezionale (a partire dal PDP-8, omnibus, 1965).

Principali vantaggi della struttura a bus singolo:

- elevata flessibilità

- bassi costi.

- $\bullet$  Problema: i dispositivi non possono trasmettere contemporaneamente.

Le architetture contengono uno o più bus che collegano questi tre componenti.

A.A. 2009-2010

6/38

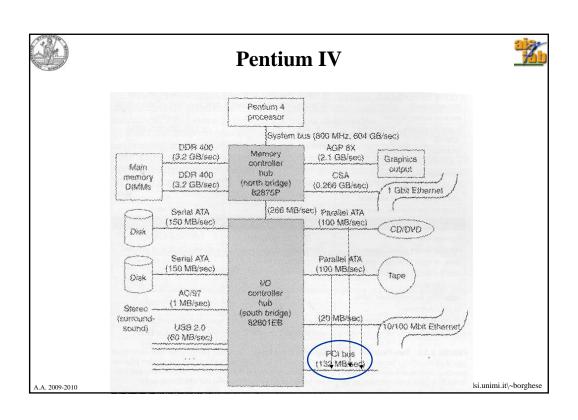

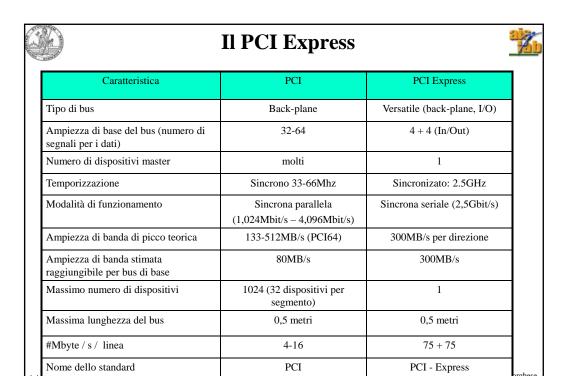

#### Caratteristica **PCI SCSI** I/O Tipo di bus Back-plane Ampiezza di base del bus (numero di 32-64 8-32 segnali per i dati) Numero di dispositivi master molti molti Temporizzazione Sincrono 33-66Mhz Asincrono o sincrono (5-20Mhz) Ampiezza di banda di picco teorica 133-512MB/s (PCI64) 5-40MB/s Ampiezza di banda stimata 80MB/s2,5-40MB/s raggiungibile per bus di base 1024 (32 dispositivi per 7-31 Massimo numero di dispositivi segmento) Massima lunghezza del bus 0,5 metri 25 metri Nome dello standard PCI ANSI X3.131

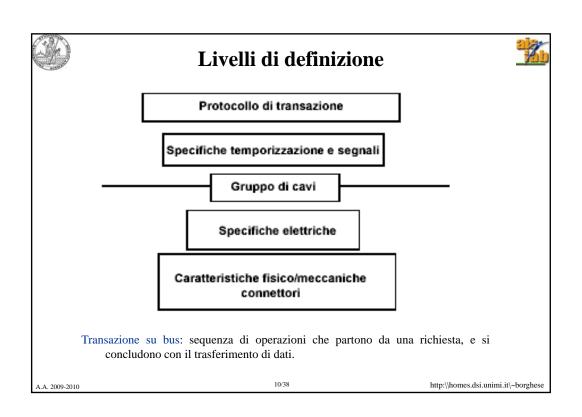

I bus

A.A. 2009-2010 13/38 http:\\homes.dsi.unimi.it\~borghese

### Caratteristiche di bus asincroni

| Caratteristiche               | Firewire (1394)                                       | USB 2.0                                                                    |

|-------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|

| Tipo di BUS                   | I/O                                                   | I/O                                                                        |

| Ampiezza bus (numero segnali) | 4                                                     | 2                                                                          |

| Clock                         | Asincrono                                             | Asincrono                                                                  |

| Picco di velocità             | 50Mbyte/s (Firewire 400)<br>100Mbyte/s (Firewire 800) | 0.2Mbye/s (low speed)<br>1.5Mbyte/s (full speed)<br>60Mbyte/s (high speed) |

| Numero massimo di<br>device   | 63                                                    | 127                                                                        |

| Nome standard                 | IEEE 1394a, 1394b                                     | USE Implementors Forum                                                     |

| Lunghezza massima             | 4.5m                                                  | 5m                                                                         |

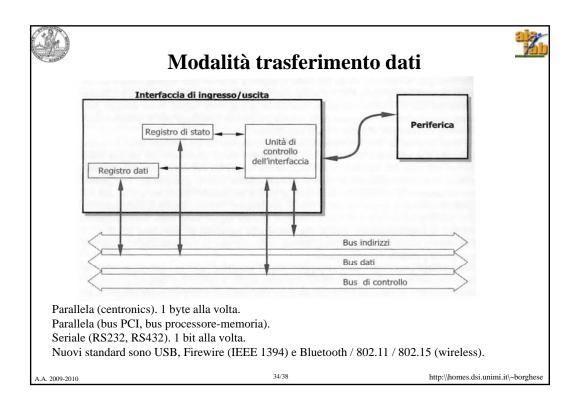

Bus seriali ad alta velocità, punto a punto, con commutazione.

A.A. 2009-2010 14/38 http:\\homes.dsi.unimi.it\~borghese

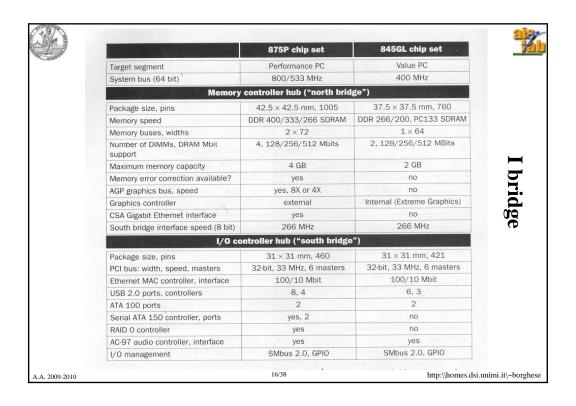

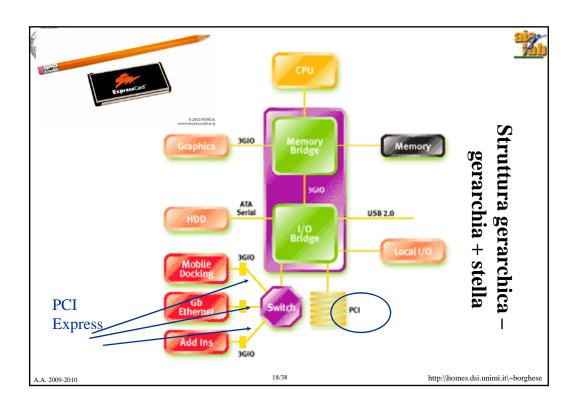

# Speciiche dei chipset

|                                    | Intel 5000P chip set   | Intel 975X chip set       | AMD 580X CrossFiret       |

|------------------------------------|------------------------|---------------------------|---------------------------|

| Target segment                     | Server                 | Performance PC            | Server/Performance PC     |

| Front Side Bus (64 bit)            | 1066/1333 MHz          | 800/1066 MHz              | _                         |

|                                    | Memory controller hu   | ıb ("north bridge")       |                           |

| Product name                       | Blackbird 5000P MCH    | 975X MCH                  |                           |

| Pins                               | 1432                   | 1202                      |                           |

| Memory type, speed                 | DDR2 FBDIMM 667/533    | DDR2 800/667/533          |                           |

| Memory buses, widths               | 4×72                   | 1×72                      |                           |

| Number of DIMMs, DRAM/DIMM         | 16, 1 GB/2 GB/4 GB     | 4, 1 GB/2 GB              |                           |

| Maximum memory capacity            | 64 GB                  | 8 GB                      |                           |

| Memory error correction available? | Yes                    | No                        |                           |

| PCIe/External Graphics Interface   | 1 PCle x16 or 2 PCle x | 1 PCle x16 or 2 PCle x8   |                           |

| South bridge interface             | PCIe x8, ESI           | PCIe x8                   |                           |

|                                    | I/O controller hub     | ("south bridge")          |                           |

| Product name                       | 6321 ESB               | ICH7                      | 580X CrossFire            |

| Package size, pins                 | 1284                   | 652                       | 549                       |

| PCI-bus: width, speed              | Two 64-bit, 133 MHz    | 32-bit, 33 MHz, 6 masters | _                         |

| PCI Express ports                  | Three PCIe x4          |                           | Two PCIe x16, Four PCI x1 |

| Ethernet MAC controller, interface | _                      | 1000/100/10 Mbit          | _                         |

| USB 2.0 ports, controllers         | 6                      | 8                         | 10                        |

| ATA ports, speed                   | One 100                | Two 100                   | One 133                   |

| Serial ATA ports                   | 6                      | 2                         | 4                         |

| AC-97 audio controller, interface  | _                      | Yes                       | Yes                       |

| I/O management                     | SMbus 2.0, GPI0        | SMbus 2.0, GPIO           | ASF 2.0, GPIO             |

# Sommario

I bus

La gestione dei bus

La gestione dell'I/O

A.A. 2009-2010

20/38

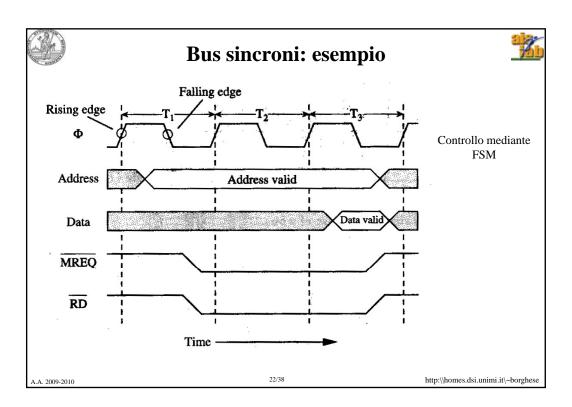

### **Bus sincroni**

- The le linee di controllo è presente la linea che porta il segnale di clock (bus clock). Esiste un

protocollo di comunicazione scandito dai cicli di clock, in generale diverso (ma sicnronizzato)

da quello della CPU.

- Questo tipo di protocollo permette di ottenere bus molto veloci.

- Svantaggi:

- ◆ Ogni device deve essere sincronizzato.

- ◆ Lunghezza limitata (per evitare che i ritardi nei fronti dovuti alla propagazione producano disallineamenti, clock skew).

- ◆ Tutti i dispositivi devono potere lavorare alla frequenza imposta dal bus clock.

- I bus processor-memory sono spesso sincroni in quanto:

- ♦ hanno dimensioni ridotte.

- ♦ hanno pochi elementi connessi.

Ciclo di bus (*bus cycle*): numero di cicli per effettuare una transazione: tipicamente da 2 a 5 cicli di bus clock.

A.A. 2009-2010 21/38 http://homes.dsi.unimi.it/~borghese

### Bus asincroni

- Un bus asincrono non è dotato di clock.

- La comunicazione tra due parti avviene mediante un protocollo di handshaking.

(!MSYN) -> Job -> (!SSYN) -> (MSYN) -> (SSYN)

- I bus asincroni possono avere lunghezza elevata per connettere molti dispositivi.

- Sono efficienti quando i tempi di esecuzione delle varie periferiche variano molto tra loro.

- Spesso i bus di I/O sono asincroni.

A. 2009-2010 23/38 http:\\homes.dsi.unimi.it\~borghese

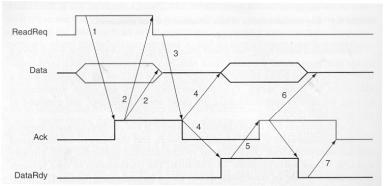

# Esempio di handshaking

**ReadReq:** segnale di controllo di MemoryRead. In corrispondenza di questo segnale l'indirizzo della parola di memoria viene inviato sul bus dati.

**Data Rdy:** viene utilizzato per indicare che la parola è pronta sulle linee di dato. Questo segnale viene inviato dalla memoria quando il dato è disponibile in uscita dalla memoria.

Ack: viene utilizzato come risposta ai 2 segnali precedenti. Feed-back.

I segnali di ReadReq e DataReady rimangono alti fino a quando il ricevente (la memoria) non ha visto il comando e letto i dati corrispondenti.

A.A. 2009-2010

24/38

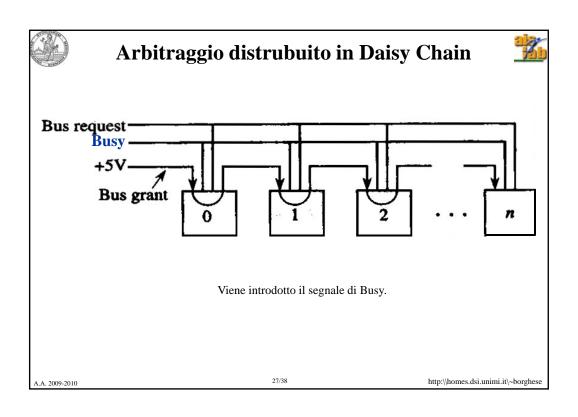

### Arbitraggio del bus

Protocollo La comunicazione su bus deve essere regolata attraverso un protocollo di comunicazione.

Viene introdotto il concetto di **bus master (padrone del bus)**, il cui scopo è quello di controllare l'accesso al bus.

L'architettura più semplice è quella che prevede un unico bus master (il processore) in cui tutte le comunicazioni vengono mediate dal processore stesso.

Questo può creare un collo di bottiglia. Ad esempio nel caso di trasferimento di dati da I/O a memoria.

Si utilizza allora un'architettura con più dispositivi master.

In questo caso occorre definire e rispettare una policy che coordini i vari dispositivi bus master. Questa policy si chiama di **arbitraggio** del bus. Un solo dispositivo alla volta può essere master, tutti gli altri ascoltano.

Questo è il principale inconveniente dei bus a nodo comune.

4. 2000 2010

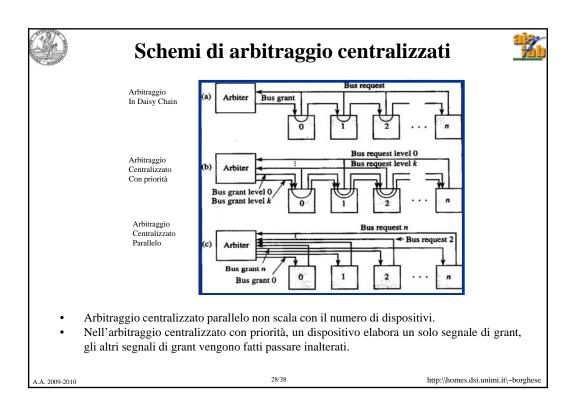

# Protocollo di arbitraggio

http:\\homes.dsi.unimi.it\~borghese

Occorre stabilire quale master autorizzare all'utilizzo del bus.

Ad ogni dispositivo viene assegnata una priorità.

Il dispositivo a priorità maggiore può accedere prima al bus.

#### Meccanismo di accesso al bus diventa:

- 1. Richiesta del bus (bus request)

- 2. Assegnamento del bus (bus grant)

Problema è assicurare una fairness.

Compromesso tra fairness e priorità.

Un arbitro si preoccupa quindi di gestire bus request e bus grant.

A.A. 2009-2010 26/

$http: \\ \ homes.dsi.unimi.it \\ \ \sim borghese$

# Arbitraggio distribuito con autoselezione

In questo schema un dispositivo che vuole prendere il controllo del bus, deve:

- 1) Inviare il segnale di richiesta del bus.

- 2) Scrivere sul bus il codice che lo identifica.

- 3) Controllare se il bus è libero.

- 4) Se il bus non è occupato ma ci sono richieste contemporanee di bus, controllare il codice dei dispositivi che hanno fatto richiesta.

- 5) Occupare il bus se è libero o i dispositivi hanno priorità minore: inviare 0 sulla linea di bus grant ai dispositivi successivi, asserisce la linea di busy (il bus è occupato), altrimenti non fare nulla. Ciascun dispositivo è arbitro.

- 6) Deasserire la richiesta del bus.

Problema: rilevamento delle collisioni. Occorre prevedere un segnale di ricevuto.

A.A. 2009-2010

29/38

http:\\homes.dsi.unimi.it\~borghese

### **Sommario**

I bus

La gestione dei bus

La gestione dell'I/O

A.A. 2009-2010 30/38 http:\\homes.dsi.unimi.it\~borghese

### I/O

Dispositivi eterogenei per:

velocità di trasferimento.

latenze.

sincronismi.

modalità di interazione (con l'uomo o con una macchina)

A.A. 2009-2010 31/38 http:\\homes.dsi.unimi.it\\~borghese

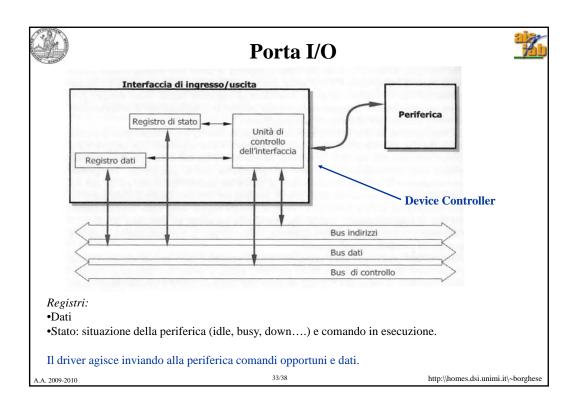

# Bus & buffer

- I dispositivi sono collegati al bus tramite porte.

- I dispositivi collegati al bus variano in termini di velocità dell'esecuzione delle operazioni ⇒ necessario un meccanismo di sincronizzazione per garantire il trasferimento efficiente delle informazioni sul bus.

- Tipicamente all'interno delle unità che utilizzano il bus sono presenti dei registri di buffer per mantenere l'informazione durante i trasferimenti e non vincolarsi alla velocità del dispositivo più lento connesso al bus.

- All'interno dell'ampiezza di banda massima si può:

- Aumentare la velocità di trasferimento. Buffer grossi.

- Ridurre i tempi di risposta (latenza). Buffer piccoli.

A.A. 2009-2010 32/38 http:\homes.dsi.unimi.it\~borghese

### Funzionamento di un driver

- CPU richiede alla periferica (controller della periferica) l'esecuzione di un'operazione di read o di write.

- 2. I dati coinvolti nell'operazione devono essere trasferiti da e verso la memoria centrale.

Per potere eseguire un'operazione di read / write, occorre spesso una serie di operazioni sul dispositivo, che vengono eseguite attraverso il controller.

Esempio: una stampante ha 1 registro dati ed 1 registro di stato. Il registro di stato contiene il bit done, che viene impostato a 1 quando il carattere è stato stampato; ed il bit error che, indica se ci sono problemi. Il processore deve controllare che non ci siano errori e che il bit di done sia stato settato ad 1 prima di inviare un altro dato.

Per potere inviare i comandi al controller, occorre prima avere individuato il controller giusto!! A ciascun dispositivo viene dato uno o più numeri -> indirizzo personalizzato.

#### 2 modalità:

- Memory-mapped

- Istruzioni speciali di I/O

.A. 2009-2010 35/38 http:\\homes.dsi.unimi.it\~borghese

### Istruzioni speciali di I/O

Istruzioni appartenente alla ISA che indirizzano direttamente il dispositivo (i registri del dispositivo):

- > Numero del dispositivo

- > Parola di comando (o indirizzo della parola che contiene il comando)

Sul bus è possibile inviare il numero del dispositivo su un insieme di linee dedicate. Ci saranno linee dedicate anche ai segnali di controllo (read / write).

I dati viaggeranno sulle linee dedicate ai dati.

Rendendo le istruzioni illegali al di fuori del kernel mode del processore, i programmi utenti non accedono direttamente ai device controller.

Esempio di architetture di questo tipo: Intel IA-32, IBM370.

AA 2009-2010 36/38 http:\\homes.dsi.unimi.it\~borghese

### Indirizzamento memory-mapped

- •I registri del device controller sono considerati come celle di memoria RAM.

- •I loro indirizzi saranno diversi da quelli delle celle di memoria.

- •Il processore esegue operazioni di I/O come se fossero operazioni di lettura/scrittura in memoria.

#### Esempio:

sw \$s0, indirizzo lw \$s0, indirizzo

dove l'indirizzo è al di fuori dallo spazio fisico della memoria.

- I controller ascoltano tutti i segnali in transito sul bus (*bus snooping*) e si attivano solamente quando riconoscono sul bus indirizzi, l'indirizzo corrispondente alla propria locazione di memoria.

- Gli indirizzi riservati ai registri del controller fanno di solito riferimento alla porzione di memoria riservata al SO e non accessibile quindi al programma utente.

- I programmi utente devono quindi passare dal SO per accedere a questi indirizzi riservati (**modalità kernel**) e quindi effettuare operazioni di I/O. Questo è quanto viene fatto ricorrendo alle System Call.

A.A. 2009-2010 37/38 http:\\homes.dsi.unimi.it\~borghese

# **Esempio: Receiver (tastiera)**

# NB i dispositivi vengono indirizzati tramite gli indirizzi "alti".

.text .globl main

li \$t0, 0x8000 0000 # indirizzo del receiver control register (2Gbyte)

li \$t2, 0x8000 0004 # indirizzo del receiver data register

# Ciclo di lettura di un carattere

ciclo: lw \$t1, 0(\$t0) # Contenuto del registro di controllo

andi \$t1, \$t1, 0x1 # if t1 = 1 esci

beq \$t1, \$zero, ciclo

lw \$a0, 0(\$t2) # Caricamento del dato in a0

li \$v0, 10 # exit

syscall

A.A. 2009-2010 38/38 http://homes.dsi.unimi.it/~borghese

# Sommario

Il bus ed il protocollo di trasferimento

Tipologie di bus

La gestione dell'I/O

AA. 2009-2010 39/38 http:\\homes.dsi.unimi.it\~borghese