# Carry look-ahead Adder & Firmware Multiplier

Prof. Alberto Borghese Dipartimento di Scienze dell'Informazione

borghese@dsi.unimi.it

Università degli Studi di Milano

Riferimenti sul Patterson: C.6 & 3.4

A.A. 2009-2010

1/41

http:\\homes.dsi.unimi.it\~borghese

#### **Sommario**

#### Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2009-2010

2/41

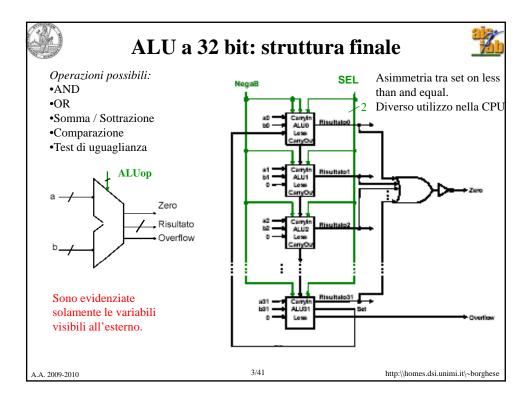

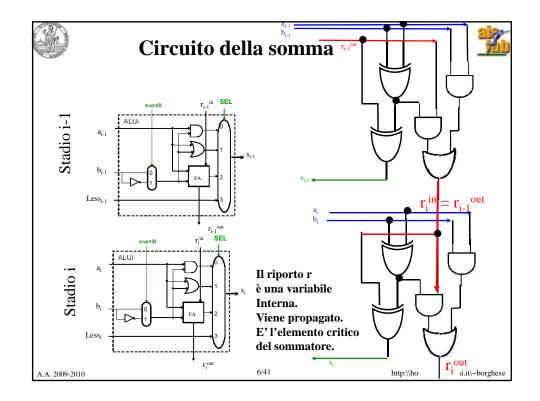

# Operazione di somma

111 ← Riporto

1011 + ← Addendo 1

110 = ← Addendo 2

-----

10001

3 Attori: addendo 1, addendo 2, riporto.

Viene eseguita sequenzialmente da dx a sx.

A.A. 2009-2010

4/41

$http: \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} http: \hspace{-0.05cm} \hspace{-0.05c$

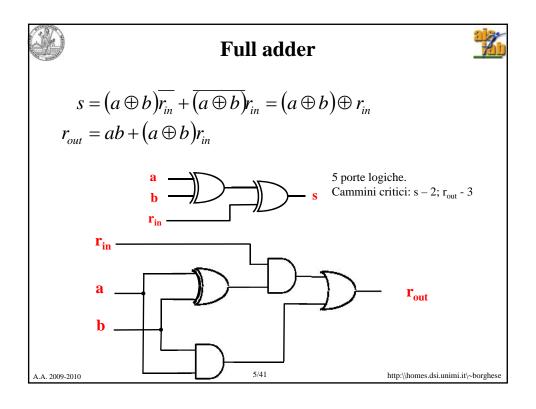

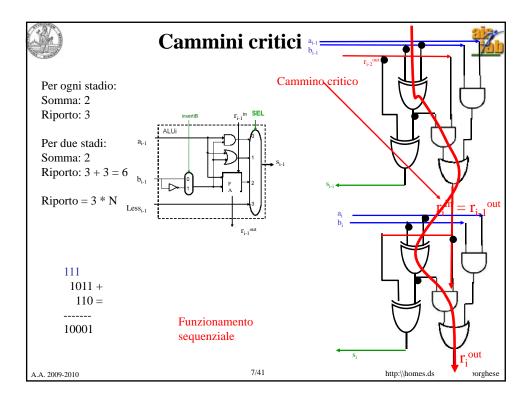

# I problemi del full-adder

Il full adder con propagazione del riporto è lento:

- Il riporto si propaga sequenzialmente caratteristica dell'algoritmo di calcolo

- la commutazione dei circuiti non è istantanea (tempo di commutazione)

caratteristica fisica dei dispositvi

Soluzioni modificare l'algortimo modificare i dispositivi

A.A. 2009-2010

8/41

$http: \hspace{-0.05cm} \hspace{-$

#### **Sommario**

Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2009-2010

9/41

http:\\homes.dsi.unimi.it\~borghese

# Prima possibilità: forma tabellare

Riscrivo le equazioni del riporto in modo non sequenziale. Come?

$$r_{out} = f(a_0, b_0, a_1, b_1, a_2, b_2, a_3, b_3,...)$$

Scrivo la tabella della verità dove in uscita ho gli N riporti ed In ingresso 2\*N valori (gli N bit dei 2 addendi).

La tabella della verità ha 2<sup>2N</sup> righe (per N=32, ...)

# Carry look-ahead (anticipazione di riporto)

Approccio strutturato per diminuire la latenza della somma.

$$\mathbf{r}_{out} = \mathbf{ab} + (\mathbf{a} \oplus \mathbf{b}) \mathbf{r}_{in}$$

#### Analisi del singolo stadio.

Quando si genera un riporto in uscita?

$r_{in}$  a b FA

Quando ho almeno due 1, in ingresso; cioè tra r<sub>in</sub>, a e b.

http:\\homes.dsi.unimi.it\~borghese

10001

A.A. 2009-2010

# Propagazione e generazione

Ho riporto quando ho almeno due 1, in ingresso; cioè tra  $r_{in}$ , a e b.

#### Osservazioni:

- Viene generato un riporto dallo stadio i, qualsiasi sia il riporto in ingresso se  $a = b = 1 \Rightarrow g_i = a_i b_i$ .

- Viene generato un riporto allo stadio i, se il riporto in ingresso è = 1 ed una delle due variabili in ingresso è = 1 =>se  $p_i = (a_i \oplus b_i) =>$  viene generato riporto se  $p_i r_i^{in} = 1$  ( $p_i$ propaga il segnale di riporto r<sub>i</sub><sup>in</sup>).

Quando sia la condizione 1) che la condizione 2) è verificata? Cosa succede se entrambe le condizioni sono verificate?

A.A. 2009-2010

12/41

$http: \\ \ \ homes. dsi. unimi. it \\ \ \ \ \ \ borghese$

### **Esempio**

Sono interessato ad  $r_4^{\text{out}}$ . Supponiamo  $r_0^{\text{in}} = 0$ .

$$r_5^{\text{in}} = r_4^{\text{out}} = 0$$

$r_5^{\text{in}} = r_4^{\text{out}} = 1$   $r_5^{\text{in}} = r_4^{\text{out}} = 1$

Per propagazione Per generazione

$$p_4 = (a_4 \oplus b_4)r_4^{\ in}.$$

$g_4 = a_4b_4$

A.A. 2009-2010 13/41 http:\\homes.dsi.unimi.it\~borghese

A.A. 2009-2010

# Sviluppo della funzione logica riporto

$http: \hspace{-0.05cm} \verb|\| homes.dsi.unimi.it| \hspace{-0.05cm} \sim \hspace{-0.05cm} borghese$

14/41

# Sviluppo della funzione logica riporto

$$r_0 = g_0 + p_0 r_0$$

$$r_1 = g_1 + p_1 r_0 = g_1 + p_1 g_0 + p_1 p_0 r_0$$

$$\mathbf{r_3} = \mathbf{g_3} + \mathbf{p_3} \mathbf{r_2} = \mathbf{g_3} + \mathbf{p_3} (\mathbf{g_2} + \mathbf{p_2} \mathbf{g_1} + \mathbf{p_2} \mathbf{p_1} \mathbf{g_0} + \mathbf{p_2} \mathbf{p_1} \mathbf{p_0} \mathbf{r_0}) = \mathbf{g_3} + \mathbf{p_3} \mathbf{g_2} + \mathbf{p_3} \mathbf{p_2} \mathbf{g_1} + \mathbf{p_3} \mathbf{p_2} \mathbf{p_1} \mathbf{g_0} + \mathbf{p_3} \mathbf{p_2} \mathbf{p_1} \mathbf{p_0} \mathbf{r_0}.$$

A.A. 2009-2010

15/4

http:\\homes.dsi.unimi.it\~borghese

$http: \hspace{-0.05cm} \verb|\| homes.dsi.unimi.it| \hspace{-0.05cm} \sim \hspace{-0.05cm} borghese$

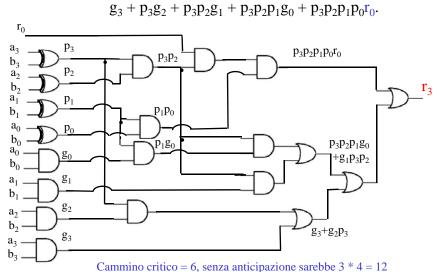

#### Determinazione del cammino critico.

$\mathbf{r_3} = \mathbf{g_3} + \mathbf{p_3} \mathbf{r_2} = \mathbf{g_3} + \mathbf{p_3} (\mathbf{g_2} + \mathbf{p_2} \mathbf{g_1} + \mathbf{p_2} \mathbf{p_1} \mathbf{g_0} + \mathbf{p_2} \mathbf{p_1} \mathbf{p_0} \mathbf{r_0}) =$

A.A. 2009-2010 16/41

# Quanto si guadagna con l'anticipazione del riporto?

Cammino critico per le variabili interne:

$$r_2^{\text{out}} = > 5$$

$$r_1^{\text{out}} => 4$$

$$r_0^{\text{out}} = > 3$$

Cammino critico per le variabili esterne:

$$r_3^{\text{out}} => 6$$

$s_3 = 6$  NB la prima porta XOR è in comune con  $r_2^{out}$

$s_2 => 5$  NB la prima porta XOR è in comune con  $r_1^{\text{out}}$

$s_2 => 4$  NB la prima porta XOR è in comune con  $r_0^{\text{out}}$

$s_0 = > 2$

A.A. 2009-2010

17/4

http:\\homes.dsi.unimi.it\~borghese

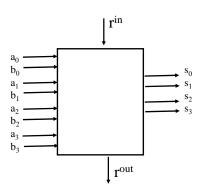

#### Addizionatori modulari

La complessità del circuito è tollerata per piccoli n.

Circuiti sommatori indipendenti si hanno per 4 bit.

Moduli elementari.

Come si ottiene la somma?

Collegando in cascata i moduli (sommatori elementari). Cammino critico = 6 \* N/4. Per 32 bit, 48.

Per confronto, senza parallelizzazione, per 32 bit, N \* 3 = 96.

A.A. 2009-2010

18/41

$http: \hspace{-0.05cm} \hspace{-$

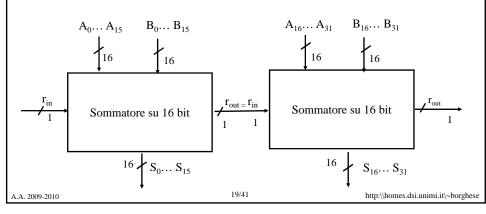

# Addizionatori modulari::esempio

Occorre sommare 2 variabili, A e B, su N = 32 bit Ho a disposizione due sommatori su 16 bit.

Come si ottiene la somma?

## **Sommario**

Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2009-2010

20/41

$http: \hspace{-0.5em} \hspace{-0.5em$

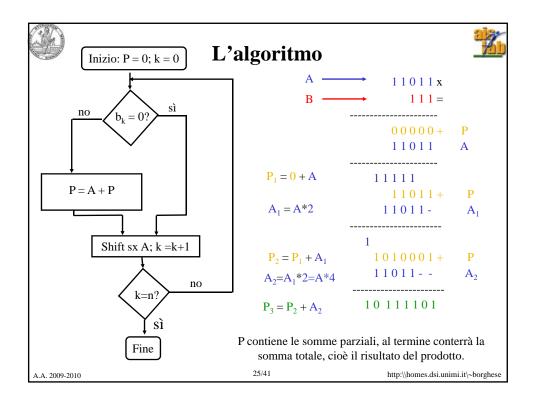

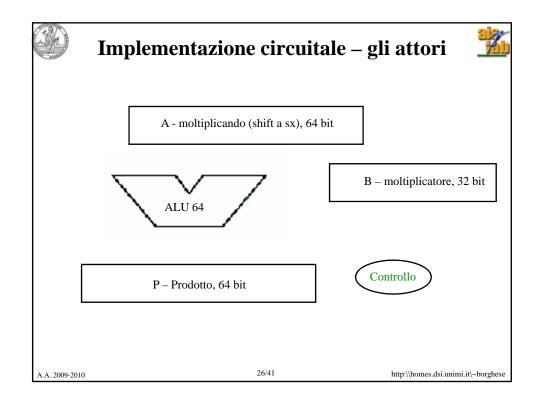

# L'approccio firmware

Nell'approccio firmware, viene inserita nella ALU una unità di controllo e dei registri. L'unità di controllo attiva opportunamente le unità aritmetiche ed il trasferimento da/verso i registri. Approccio "controllore-datapath".

Viene inserito un microcalcolatore dentro la ALU.

Il primo microprogramma era presente nell'IBM 360 (1964).

A.A. 2009-2010 21/41 http:\\homes.dsi.unimi.it\~borghese

## **Shift (scalamento)**

Dato A su 32 bit:  $a_i = a_{i-k}$  k shift amount (>, =, < 0).

Effettuato al di fuori delle operazioni selezionate dal Mux della ALU, da un circuito denominato Barrel shifter.

Tempo comparabile con quello della somma.

Operazioni codificate in modo specifico nell'ISA.

Il bit a<sub>0</sub> si "perde". Il bit  $a_n = 0$ .

A.A. 2009-2010

http:\\homes.dsi.unimi.it\~borghese

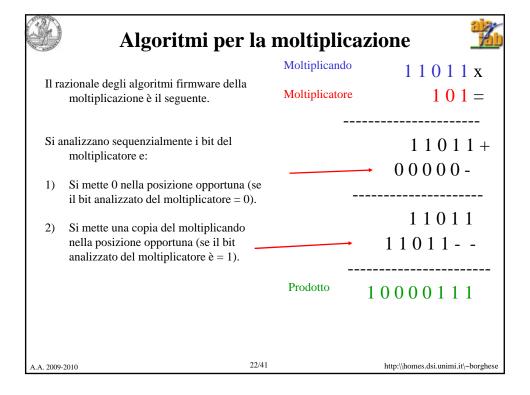

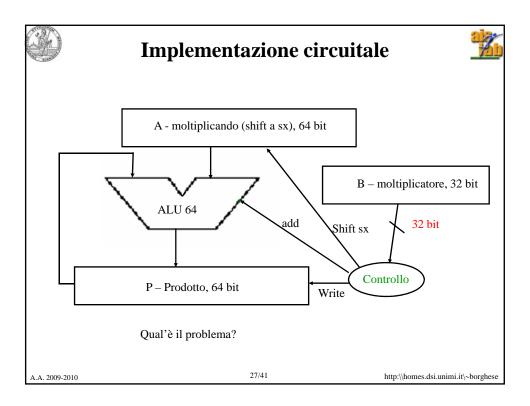

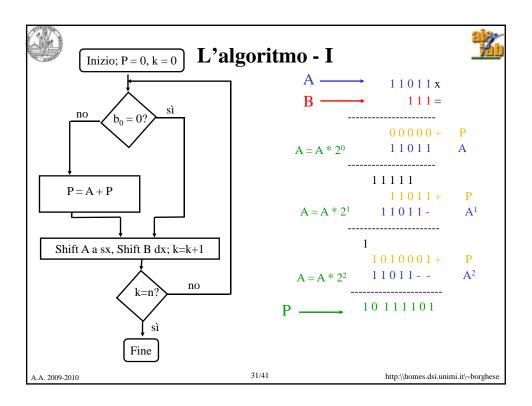

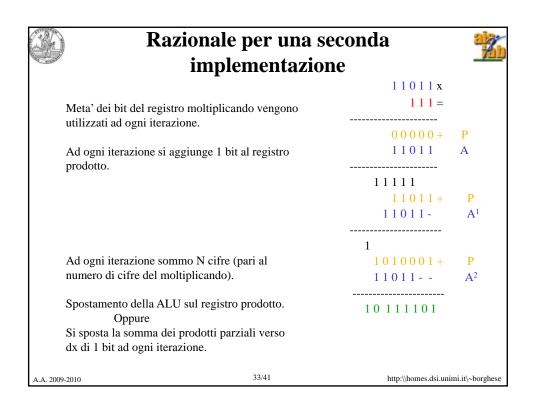

# Moltiplicazione utilizzando somma e shift

$1\ 1\ 0\ 1\ 1\ x$ Utilizzo un registro prodotto da 64 bit, inizializzato a 0.

1 1 1 =

$0\ 0\ 0\ 0\ 0\ +$

Itero per ogni bit del moltiplicatore:

11011

A) Sommo il moltiplicando al prodotto se il bit = 1. 1101

11111

B) Shift a sx di un bit il moltiplicando (A' = A \* base).

$1\ 0\ 1\ 0\ 0\ 0\ 1\ +$ 11011--

$1\; 0\;\; 1\; 1\; 1\; 1\; 0\; 1$

A.A. 2009-2010

#### **Esercizi**

Costruire il circuito HW che esegui la moltiplicazione 7 x 9 in base 2.

Eseguire la stessa moltiplicazione secondo l'algoritmo visto, indicando passo per passo il contenuto dei 3 componenti: A che contiene il moltiplicando, B che contiene il moltiplicatore e P che contiene somme parziali ed il risultato finale.

A.A. 2009-2010

28/41

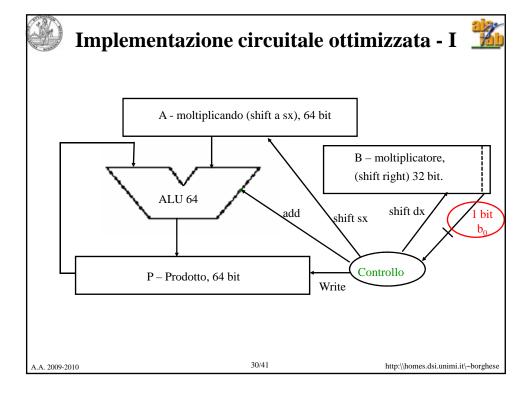

#### **Sommario**

Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2009-2010

29/41

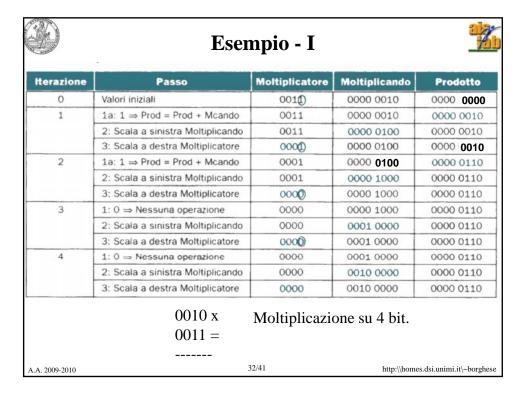

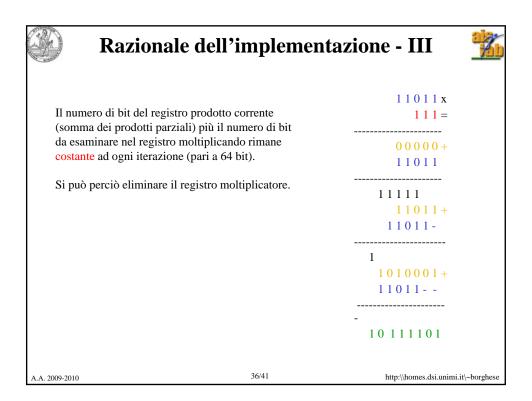

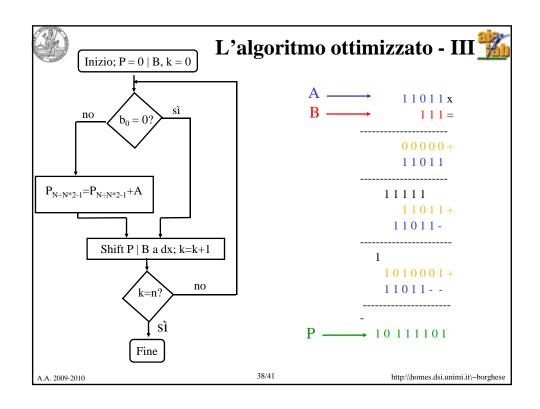

# Esempio di esecuzione dell'algoritmo ottimizzato - III

http:\\homes.dsi.unimi.it\~borghese

| Iterazione | Passo                        | Moltiplicando | Prodotto    |

|------------|------------------------------|---------------|-------------|

| 0          | Valori iniziali              | 0010          | 0000 001(1) |

| 1          | 1a: 1 ⇒ Prod = Prod + Mcando | 0010          | 0010 0011   |

|            | 2: Scala a destra Prodotto   | 0010          | 0001 0000   |

| 2          | 1a: 1 ⇒ Prod = Prod + Mcando | 0010          | 0011 0001   |

|            | 2: Scala a destra Prodotto   | 0010          | 0001 1000   |

| 3          | 1: 0 ⇒ Nessuna operazione    | 0010          | 0001 1000   |

|            | 2: Scala a destra Prodotto   | 0010          | 0000 1100   |

| 4          | 1: 0 ⇒ Nessuna operazione    | 0010          | 0000 1100   |

|            | 2: Scala a destra Prodotto   | 0010          | 0000 0110   |

Il moltiplicando è allineato (e sommato) ai bit più significativi del prodotto.

A.A. 2009-2010

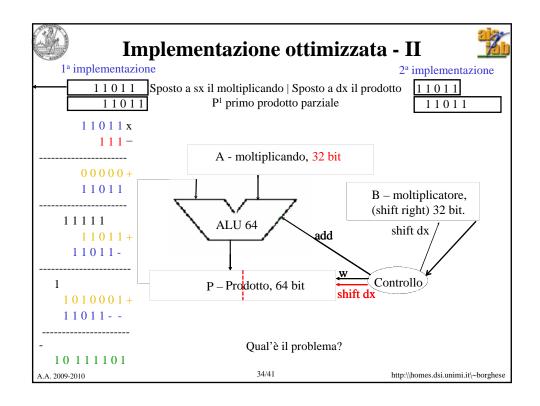

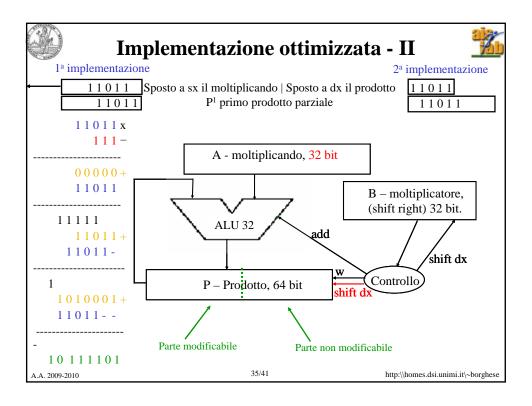

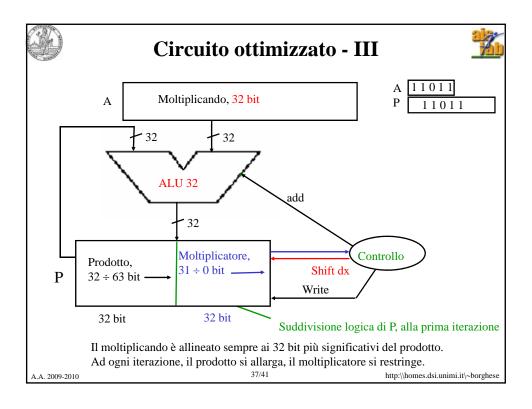

Circuito finale – moltiplicatore firmware 11011 Moltiplicando, 32 bit A 11011 **-** 32 32 ALU 32 add 32 Moltiplicatore, Controllo Prodotto,  $31 \div 0$  bit. Shift dx  $32 \div 63 \text{ bit } -$ Write 32 bit 32 bit Suddivisione logica di P, alla prima iterazione bit 64 – per evitare overflow Le somme parziali possono occupare un bit in più per nelle somme parziali effetto del riporto. 40/41 A.A. 2009-2010 http:\\homes.dsi.unimi.it\~borghese

# Sommario

Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2009-2010

41/41

$http: \\ \ \ homes.dsi.unimi.it \\ \ \ \sim borghese$