## La seconda forma canonica Circuiti notevoli

Prof. Alberto Borghese Dipartimento di Scienze dell'Informazione

borghese@dsi.unimi.it

Università degli Studi di Milano

Riferimenti: Sezione C3.

A.A. 2009-2010

1/41

http:\\homes.dsi.unimi.it\~borghese

## **Sommario**

Implementazione circuitale mediante PLA o ROM.

La seconda forma canonica.

Circuiti combinatori notevoli

A.A. 2009-2010

2/41

#### Circuiti combinatori

- Circuiti logici digitali in cui le operazioni (logiche) dipendono solo da una combinazione degli input.

- Circuiti senza memoria. Ogni volta che si inseriscono in ingresso gli stessi valuri, si ottengono le stesse uscite. Il risultato non dipende dallo stato del circuito.

- I circuiti combinatori descrivono delle funzioni Booleane. Queste funzioni si ottengono combinando tra loro (in parallelo o in cascata) gli operatori logici: NOT, AND, OR.

- Il loro funzionamento può essere descritto come tabella della verità.

- Come nelle funzioni algebriche, il risultato è aggiornato immediatamente dopo il

cambiamento dell'input (si suppone il tempo di commutazione trascurabile, tempo di attesa

prima di guardare l'output sufficientemente ampio per permettere a tutti i circuiti la

commutazione).

A.A. 2009-2010 3/41 http://homes.dsi.unimi.it/~borghese

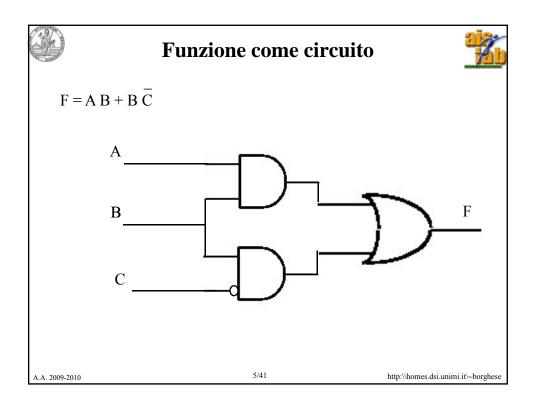

## Funzione come espressione logica

$$F = AB + B\bar{C}$$

|       |         | _       |   |

|-------|---------|---------|---|

| ABC   | A and B | B and C | F |

| 0 0 0 | 0       | 0       | 0 |

| 0 0 1 | 0       | 0       | 0 |

| 0 1 0 | 0       | 1       | 1 |

| 0 1 1 | 0       | 0       | 0 |

| 1 0 0 | 0       | 0       | 0 |

| 1 0 1 | 0       | 0       | 0 |

| 1 1 0 | 1       | 1       | 1 |

| 1 1 1 | 1       | 0       | 1 |

A.A. 2009-2010 4/41

$http: \\ \ homes.dsi.unimi.it \\ \ \ \ borghese$

# Razionale della prima forma canonica

$$F = AB + B\overline{C} = \overline{A}B\overline{C} + AB\overline{C} + ABC$$

| ABC   | F | F = 1             |

|-------|---|-------------------|

| 0 0 0 | 0 |                   |

| 0 0 1 | 0 | iif               |

| 0 1 0 | 1 | •••               |

| 0 1 1 | 0 | A = 0 B = 1 C = 0 |

| 1 0 0 | 0 | OR                |

| 1 0 1 | 0 | A = 1 B = 1 C = 0 |

| 1 1 0 | 1 | OR                |

| 1 1 1 | 1 | A = 1 B = 1 C = 1 |

|       |   | A-1B-1C-1         |

A.A. 2009-2010

# Manipolazione algebrica della prima forma canonica

$$F = \overline{ABC} + AB\overline{C} + ABC =$$

La prima forma canonica non è la rappresentazione più compatta della funzione, ma è facilmente ottenibile. Per ottenere una forma più compatta occorre semplificare.

$$F = AB(C + \overline{C}) + \overline{ABC} = AB + \overline{ABC} = B(A + \overline{AC}) = B(A + \overline{C}) =$$

$$AB + B\overline{C}$$

Verifichiamo attraverso la proprietà distributiva dell'OR rispetto all'AND che:

A A 2009 2010

$$A + \overline{AC} = (A + \overline{A})(A + \overline{C}) = A + \overline{C}$$

http:\\homes.dsi.unimi.it\~borghese

## Forme canoniche

- Esiste un metodo per ricavare automaticamente un circuito che implementi una tabella di verità?

- Esistono 2 forme canoniche (equivalenti) che garantiscono di poter realizzare una qualunque tabella di verità con solo due livelli di porte OR, AND e NOT:

- 1) Somme di Prodotti (SOP)

$$F = \sum_{i=1}^{Q} m_i$$

$$F = \overline{A} B \overline{C} + A B \overline{C} + A B C$$

2) Prodotti di Somme (POS)

# Tipi di circuiti che implementano le SOP

In generale abbiamo funzioni logiche booleane multi-input / multi-output.

- Logica distrubuita.

- PLA: Programmable Logic Array: matrici regolari AND e OR in successione, personalizzabili dall'utente.

- ROM: Read Only Memory circuiti ad hoc che implementano una particolare funzione in modo irreversibile.

A.A. 2009-2010

9/41

http:\\homes.dsi.unimi.it\~borghese

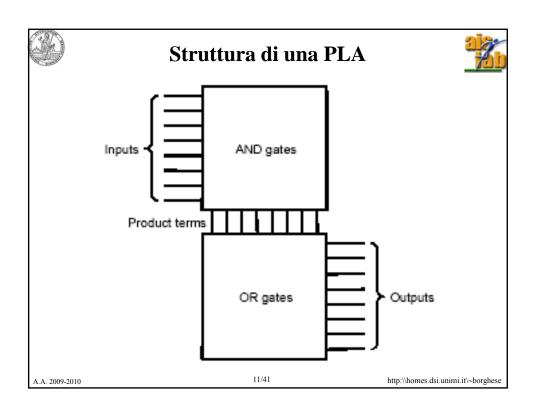

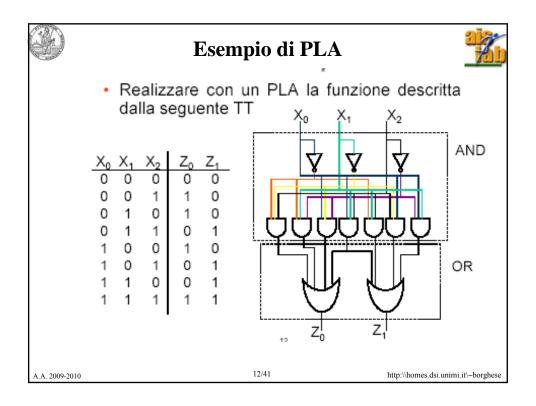

## PLA (Programmable Logica Array)

- La matrice degli AND ha n linee di ingresso: ciascuna porta ha in ingresso le n linee e il loro complemento.

- L'utente fornisce la matrice che dice quale linea entra (e come) in quale porta AND:

Crea la matrice dei mintermini, bruciando in ingresso alle porte AND le linee che non servono.

- Le uscite della matrice AND entrano nella matrice OR programmata come la precedente in base ad un'altra matrice fornita dall'utente

Si utilizza una porta OR per ogni funzione calcolata.

A.A. 2009-2010

10/41

$http: \\ \ homes. dsi. unimi. it \\ \ \ \ borghese$

#### Esercizi sulla PLA

Realizzare mediante PLA con 3 ingressi con il numero adeguato di linee interne:

- •la funzione maggioranza.

- •la funzione che vale 1 se e solo se 1 solo bit di ingresso vale 1

- •un decoder

- •la funzione che vale 0 se l'input è pari, 1 se dispari

- •la funzione che calcola i multipli di 3 (con 4

- •ingressi)

A.A. 2009-2010

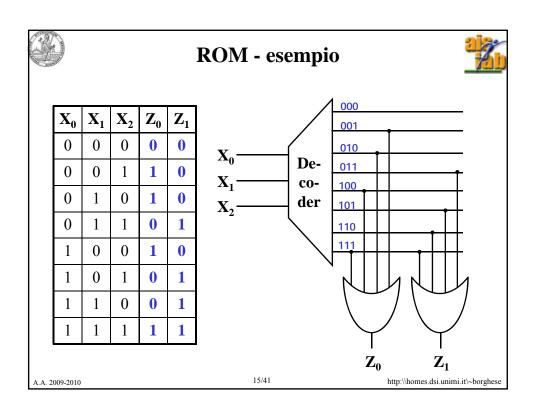

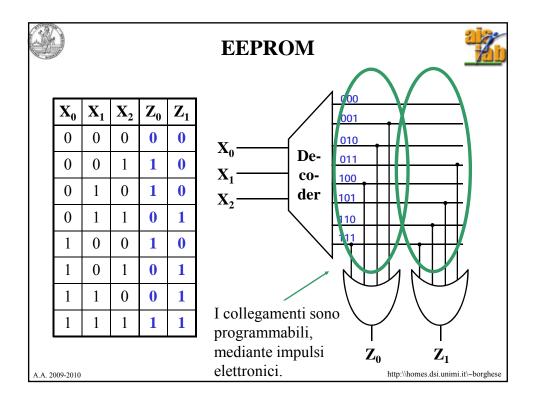

- Read Only Memory, memoria di sola lettura.

Funge anche da modulo combinatorio a uscita multipla.

- n linee di ingresso, m linee di uscita (ampiezza) a ciascuna delle 2<sup>n</sup> (altezza) configurazioni di ingresso (parole di memoria) è associata permanentemente una combinazione delle m linee di uscita.

- l'input seleziona la parola da leggere di m bit, che appare in uscita

- realizzato con un decoder n-a-2<sup>n</sup> seguito da una matrice di m porte OR.

A.A. 2009-2010 14/-

#### Confronto PLA - ROM

ROM – fornisce un'uscita per ognuna delle combinazioni degli ingressi. Decoder con 2<sup>n</sup> uscite, dove n è il numero di variabili in ingresso alla ROM. Crescita esponenziale delle uscite.

- approccio più generale. Può implementare una qualsiasi funzione, dato un certo numero di input e output.

PLA – contiene solamente i mintermini in uscita al primo stadio. Il loro numero cresce meno che esponenzialmente.

FPGA – connettività libera. Non è una struttura a 2 livelli.

A.A. 2009-2010

17/41

http:\\homes.dsi.unimi.it\~borghese

#### **Sommario**

Implementazione circuitale mediante PLA o ROM.

La seconda forma canonica.

Circuiti combinatori notevoli.

## Prima forma canonica

$$F = AB + B\overline{C} = \overline{A}B\overline{C} + AB\overline{C} + ABC$$

| ABC   | F | F = 1                      |

|-------|---|----------------------------|

| 0 0 0 | 0 | $\mathbf{r} - \mathbf{r}$  |

| 0 0 1 | 0 | iif                        |

| 0 1 0 | 1 | III                        |

| 0 1 1 | 0 | A = 0 B = 1 C = 0          |

| 1 0 0 | 0 | R = 0 B $= 1$ C $= 0$ $OR$ |

| 1 0 1 | 0 | A = 1 B = 1 C = 0          |

| 1 1 0 | 1 | OR                         |

| 1 1 1 | 1 | A = 1 B = 1 C = 1          |

|       |   | A - 1 D - 1 C - 1          |

A.A. 2009-2010 19/41 http:\\homes.dsi.unimi.it\~borghese

# Razionale della seconda forma canonica

$$F = \overline{A} B \overline{C} + A B \overline{C} + A B C$$

#### F = 1

| ABC   | F | iif                       |

|-------|---|---------------------------|

| 0 0 0 | 0 |                           |

| 0 0 1 | 0 | NOT $(A = 0 B = 0 C = 0)$ |

| 0 1 0 | 1 | AND                       |

| 0 1 1 | 0 | NOT $(A = 0 B = 0 C = 1)$ |

| 1 0 0 | 0 | AND                       |

| 1 0 1 | 0 | NOT $(A = 0 B = 1 C = 1)$ |

| 1 1 0 | 1 | AND                       |

| 1 1 1 | 1 | NOT $(A = 1 B = 0 C = 0)$ |

|       |   | AND                       |

|       |   | NOT $(A = 1 B = 0 C = 1)$ |

A.A. 2009-2010 20/41 http://homes.dsi.unimi.it/~borghese

## Verso la seconda forma canonica

|                                                    |                       | Maxtermine, M <sub>j</sub> ,: e' un prodotto di <u>tutte</u> le variabili di ingresso al quale corr <u>isponde</u> |

|----------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------|

| ABC                                                | F                     | un valore 0 per la funzione. (e.g. A B C).                                                                         |

| 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1 | 0<br>0<br>1<br>0<br>0 | j indica il numero progressivo in base 10.  Possibile espressione della seconda forma canonica:                    |

| 1 1 0 1 1 1 1                                      | 1<br>1                | $W \le 2^{N}$ $Q + W = 2^{N}$ $F = \prod_{i} \overline{M}_{i}$                                                     |

Solo AND?

$$F = (\overline{A} \overline{B} \overline{C}) (\overline{A} \overline{B} C) (\overline{A} B C) (\overline{A} \overline{B} \overline{C}) (\overline{A} \overline{B} C)$$

A.A. 2009-2010

21/41

http:\\homes.dsi.unimi.it\~borghese

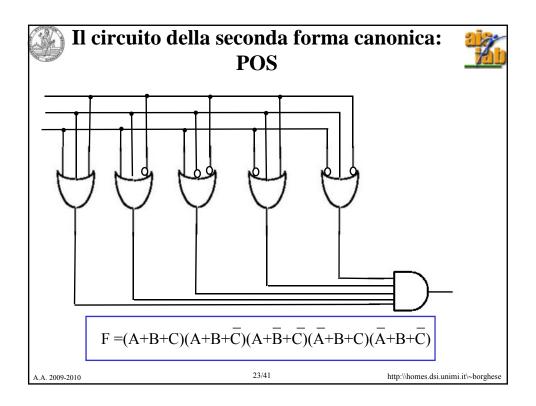

# La seconda forma canonica: prodotto di somme

F = (A+B+C)(A+B+C)(A+B+C)(A+B+C)(A+B+C)

F = 1 quando nessun fattore si annulla

A.A. 2009-2010

22/41

$http: \hspace{-0.05cm} \verb|\| homes.dsi.unimi.it| \hspace{-0.05cm} \sim borghese$

# Regole manipolazione algebrica

| Doppia Inversione                     | = x = x                 |                           |  |  |

|---------------------------------------|-------------------------|---------------------------|--|--|

| 11                                    | AND                     | OR                        |  |  |

| Identità                              | 1 x = x                 | 0 + x = x                 |  |  |

| Elemento nullo                        | 0 x = 0                 | 1 + x = 1                 |  |  |

| Idempotenza                           | x x = x                 | x + x = x                 |  |  |

| Inverso                               | $x \overline{x} = 0$    | $x + \overline{x} = 1$    |  |  |

| Commutativa                           | x y = y x               | x + y = y + x             |  |  |

| Associativa                           | (x y) z = x (y z)       | (x+y)+z=x+(y+z)           |  |  |

| AND rispetto ad OR OR rispetto ad AND |                         |                           |  |  |

| Distributiva                          | x(y+z) = xy + xz        | x + y z = (x + y) (x + z) |  |  |

| Assorbimento                          | $x\left( x+y\right) =x$ | x + x y = x               |  |  |

| Do Morgan                             |                         |                           |  |  |

| De Morgan                             | xy = x + y              | x + y = x y               |  |  |

Si possono dimostrare sostituendo 0/1 alle variabili.

A.A. 2009-2010 24/41 http:\\homes.dsi.unimi.it\~borghese

# Dalla seconda alla prima forma canonica

$$F = \prod_{i=1}^{W} \overline{M_i} = \overline{\sum_{i=1}^{W} M_i} \qquad F = AB + B\overline{C}$$

AB(C + !C) + (!A)B(!C) = ABC + AB(!C) + (!A)B(!C)

## Esempio 2

$$F = \overline{ABC} + \overline{ABC} = \overline{AC}$$

| $F = \overline{M}_1 \overline{M}_3 \overline{M}_4 \overline{M}_5 \overline{M}_6 \overline{M}_7$ |

|-------------------------------------------------------------------------------------------------|

| 1 141 1413 1414 1415 1416 1417                                                                  |

|                                                                                                 |

|                                                                                                 |

| F=(A+B+C)(A+B+C)(A+B+C)(A+B+C)(A+B+C)(A+B+C)                                                    |

|                                                                                                 |

|                                                                                                 |

26/41

A.A. 2009-2010

## **Sommario**

Implementazione circuitale mediante PLA o ROM.

La seconda forma canonica.

Circuiti combinatori notevoli.

A.A. 2009-2010

27/4

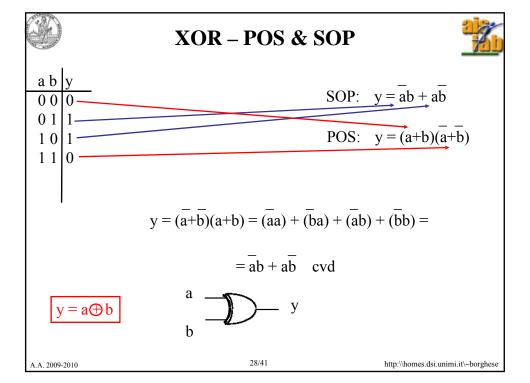

# Uscite indifferenti di un tabella delle verità

Diminuisce il numero di porte e si accorcia il cammino critico.

A.A. 2009-2010

29/4

http:\\homes.dsi.unimi.it\~borghese

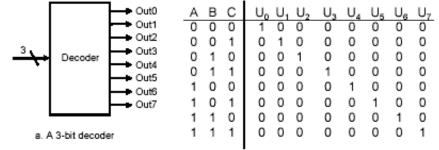

## **Decodificatore** (decoder)

- E' caratterizzato da n linee di input e 2<sup>n</sup> linee di output

- il numero binario espresso dalla configurazione delle linee di input è usato per asserire la sola linea di output di ugual indice.

- es.: con 4 linee di input e 16 di output (da 0 a 15), se in ingresso arriva il valore 0110, in uscita si alza la linea di indice 5 (la sesta!).

- utilizzato per indirizzare la memoria (cf. ROM).

A.A. 2009-2010

30/41

#### La funzione decoder

## Decoder

Le funzioni di uscita sono 2<sup>n</sup> per n input:

$$U_0 = \sim A \sim B \sim C$$

...

$$U_j = m_j$$

$$U_7 = A BC$$

A.A. 2009-2010 31/41 http://homes.dsi.unimi.it/~borghese

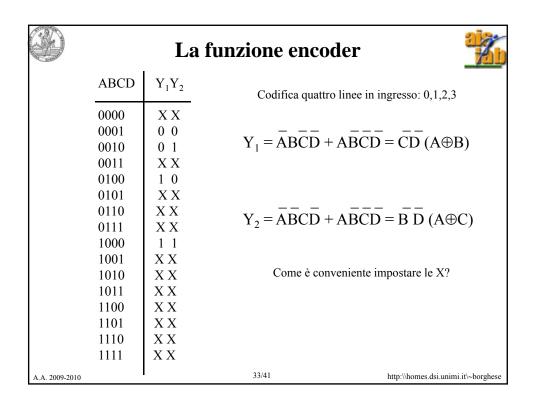

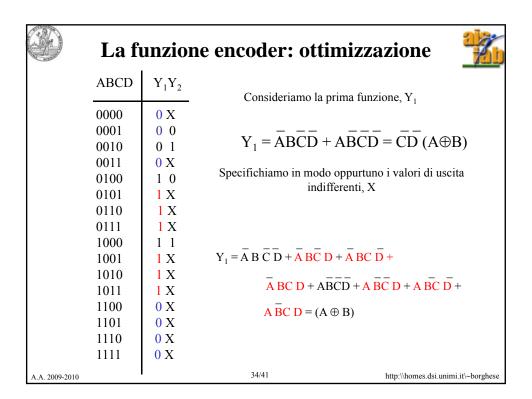

## **Codificatore** (encoder)

- $\bullet$  E' caratterizzato da n linee di input e ceil( $\log_2 n$ ) linee di output

- Una sola linea di ingresso può essere attiva.

- il numero binario espresso dalla configurazione delle linee di output rappresenta la linea di ingresso attiva.

- es.: con 16 linee di input e 4 di output, se in ingresso arriva il valore 0000 0100 0000 0000, in uscita leggiamo il numero 10.

A.A. 2009-2010

32/41

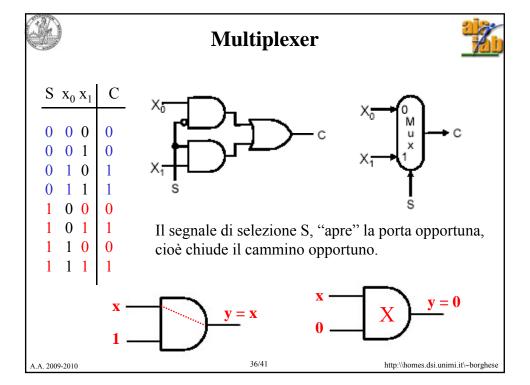

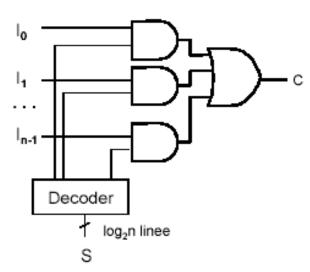

## Multiplexer

- E' caratterizzato da n linee di input (data),

- k linee di controllo (selezione).

- In base alla linea di controllo viene connessa all'uscita la linea di ingresso selezionata (cf. ROM).

- Quante linee di controllo, k, servono?

$$k = ceil (log_2 n)$$

Esempio: con 4 linee di input (da 0 a 3), se sulle linee di controllo c'è 11, in uscita si avrà il valore presente sulla linea 3

A.A. 2009-2010

35/41

#### Sintesi della funzione Mux

$$C=x_1 \left\{ \begin{array}{ccc|c} 1 & 0 & 0 & 0 \\ 1 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 \end{array} \right.$$

A.A. 2009-2010

# 🕽 Sintesi della funzione Mux nella forma POS

A.A. 2009-2010

## Mux a più vie.

Una sola porta alla volta viene aperta dal segnale S. Le porte sono mutuamente esclusive.

A.A. 2009-2010

39/41

http:\\homes.dsi.unimi.it\~borghese

# Comparatore

- E' caratterizzato da 2 insiemi di n linee di ingresso ciascuna e un output.

- L'output vale 1 se i due insiemi di bit hanno uguale valore, 0 se sono diversi.

| A <sub>0</sub> B <sub>0</sub> | Co | A <sub>1</sub> B <sub>1</sub> | C <sub>1</sub> |                             |

|-------------------------------|----|-------------------------------|----------------|-----------------------------|

| 0 0                           | 1  | 0 0                           | 1              | $C = C_0 C_1 \dots C_{n-1}$ |

| 0 0                           | 0  | 0 1                           | 0              |                             |

| 1 0                           | 0  | 1 0                           | 0              | C Ol-                       |

| 1 0<br>1 1                    | 1  | 0 1<br>1 0<br>1 1             | 1              | $C_k = a_k \oplus b_k$      |

|                               |    | l                             |                |                             |

A.A. 2009-2010

40/41

## Sommario

Implementazione circuitale mediante PLA o ROM.

La seconda forma canonica.

Circuiti combinatori notevoli.

A.A. 2009-2010

41/4

$http: \\ \ homes. dsi. unimi. it \\ \ \ \ borghese$