# Carry look-ahead Adder & Firmware Multiplier

Prof. Alberto Borghese Dipartimento di Scienze dell'Informazione

borghese@dsi.unimi.it

Università degli Studi di Milano

Riferimenti sul Patterson: B.6 & 3.4

A.A. 2006-2007

1/37

$http: \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} \hspace{-0.05cm} http: \hspace{-0.05cm} \hspace{-0.05c$

#### **Sommario**

#### Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

### I problemi del full-adder

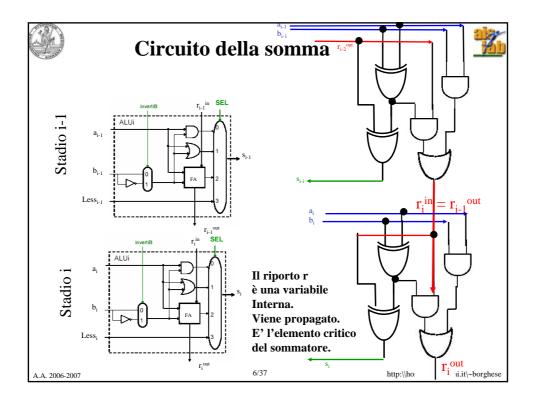

Il full adder con propagazione del riporto è lento:

- Il riporto si propaga sequenzialmente caratteristica dell'algoritmo di calcolo

- la commutazione dei circuiti non è istantanea (tempo di commutazione)

caratteristica fisica dei dispositvi

Soluzioni modificare l'algortimo modificare i dispositivi

A.A. 2006-2007

8/37

$http: \hspace{-0.05cm} \hspace{-$

#### Sommario

Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2006-2007

9/37

http:\\homes.dsi.unimi.it\~borghese

# Prima possibilità: forma tabellare

Riscrivo le equazioni del riporto in modo non sequenziale. Come?

$r_{out} = f(a_0, b_0, a_1, b_1, a_2, b_2, a_3, b_3,...)$

Scrivo la tabella della verità dove in uscita ho gli N riporti ed In ingresso 2\*N valori (gli N bit dei 2 addendi).

# Carry look-ahead (anticipazione di riporto)

Approccio strutturato per diminuire la latenza della somma.

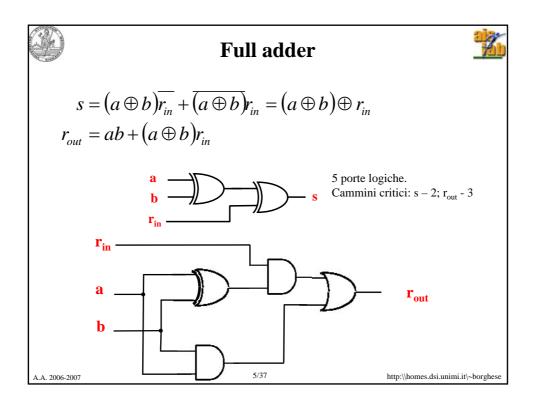

$$\mathbf{r}_{out} = a\mathbf{b} + (a \oplus \mathbf{b}) \mathbf{r}_{in}$$

#### Analisi del singolo stadio.

Quando si genera un riporto in uscita?

Quando ho almeno due 1, in ingresso; cioè tra r<sub>in</sub>, a e b.

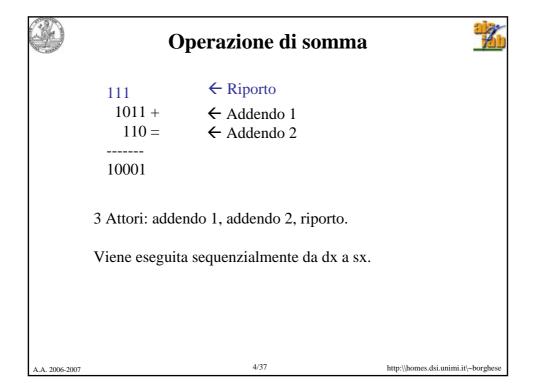

#### 11000 riporto 1101 +

100 =

10001

http:\\homes.dsi.unimi.it\~borghese

A.A. 2006-2007

### Propagazione e generazione

Ho riporto quando ho almeno due 1, in ingresso; cioè tra  $r_{in}$ , a e b.

#### Osservazioni:

- Viene generato un riporto dallo stadio i, qualsiasi sia il riporto in ingresso se  $a = b = 1 \Rightarrow g_i = a_i b_i$ .

- Viene generato un riporto allo stadio i, se il riporto in ingresso è = 1 ed una delle due variabili in ingresso è = 1  $=> p_i = (a_i \oplus b_i)r_i^{in}$ .(pi propaga il segnale di riporto  $r_i^{in}$ ).

Quando sia la condizione 1) che la condizione 2) è verificata? Cosa succede se entrambe le condizioni sono verificate?

A.A. 2006-2007

#### **Esempio**

Sono interessato ad  $r_4^{\text{out}}$ . Supponiamo  $r_0^{\text{in}} = 0$ .

$$r_5^{in} = r_4^{out} = 0$$

$$r_{\epsilon}^{in} = r_{\star}^{out} = 1$$

$$r_5^{\text{in}} = r_4^{\text{out}} = 1$$

$r_5^{\text{in}} = r_4^{\text{out}} = 1$

Per propagazione Per generazione

$$p_4 = (a_4 \oplus b_4) r_4^{\text{in}}.$$

$g_4 = a_4 b_4$

A.A. 2006-2007

http:\\homes.dsi.unimi.it\~borghese

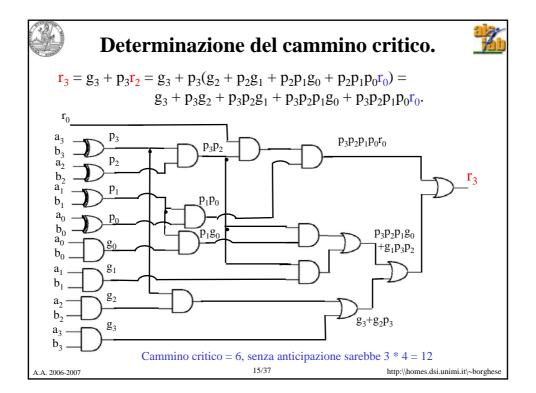

#### Sviluppo della funzione logica riporto

$$\mathbf{r_0} = \mathbf{g_0} + \mathbf{p_0}\mathbf{r_0}$$

$$\mathbf{r_1} = \mathbf{g_1} + \mathbf{p_1} \mathbf{r_0} = \mathbf{g_1} + \mathbf{p_1} \mathbf{g_0} + \mathbf{p_1} \mathbf{p_0} \mathbf{r_0}$$

$$\mathbf{r_2} = \mathbf{g_2} + \mathbf{p_2} \mathbf{r_1} = \mathbf{g_2} + \mathbf{p_2} (\mathbf{g_1} + \mathbf{p_1} \mathbf{g_0} + \mathbf{p_1} \mathbf{p_0} \mathbf{r_0}) = \mathbf{g_2} + \mathbf{p_2} \mathbf{g_1} + \mathbf{p_2} \mathbf{p_1} \mathbf{g_0} + \mathbf{p_2} \mathbf{p_1} \mathbf{p_0} \mathbf{r_0}.$$

$$\begin{aligned} \mathbf{r_3} &= \mathbf{g_3} + \mathbf{p_3} \mathbf{r_2} = \mathbf{g_3} + \mathbf{p_3} (\mathbf{g_2} + \mathbf{p_2} \mathbf{g_1} + \mathbf{p_2} \mathbf{p_1} \mathbf{g_0} + \mathbf{p_2} \mathbf{p_1} \mathbf{p_0} \mathbf{r_0}) = \\ & \mathbf{g_3} + \mathbf{p_3} \mathbf{g_2} + \mathbf{p_3} \mathbf{p_2} \mathbf{g_1} + \mathbf{p_3} \mathbf{p_2} \mathbf{p_1} \mathbf{g_0} + \mathbf{p_3} \mathbf{p_2} \mathbf{p_1} \mathbf{p_0} \mathbf{r_0}. \end{aligned}$$

A.A. 2006-2007

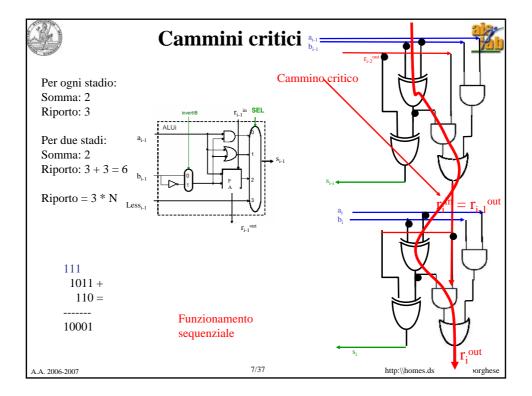

## Quanto si guadagna con l'anticipazione del 🍇 riporto?

Cammino critico per le variabili interne:

$r_2^{\text{out}} = > 5$

$r_1^{\text{out}} => 4$

$r_0^{\text{out}} = > 3$

Cammino critico per le variabili esterne:

$r_3^{\text{out}} = > 6$

$s_3 => 6$  NB la prima porta XOR è in comune con  $r_2^{out}$

$s_2 => 5$  NB la prima porta XOR è in comune con  $r_1^{out}$

$s_2 => 4$  NB la prima porta XOR è in comune con  $r_0^{\text{out}}$

=> 2

A.A. 2006-2007

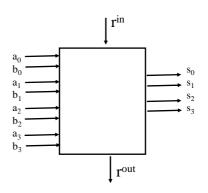

#### Addizionatori modulari

La complessità del circuito è tollerata per piccoli n.

Circuiti sommatori indipendenti si hanno per 4 bit.

Moduli elementari.

Come si ottiene la somma?

Collegando in cascata i moduli (sommatori elementari). Cammino critico = 6 \* N/4. Per 32 bit, 48. Per confronto, senza parallelizzazione, per 32 bit, N \* 3 = 96.

A.A. 2006-2007

17/37

http:\\homes.dsi.unimi.it\~borghese

#### **Sommario**

Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2006-2007

18/37

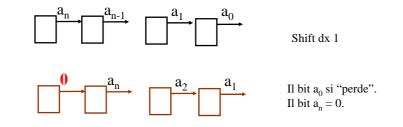

#### Shift (scalamento)

Dato A su 32 bit:  $a_j = a_{j-k}$  k shift amount (>, =, < 0).

Effettuato al di fuori delle operazioni selezionate dal Mux della ALU, da un circuito denominato *Barrel shifter*.

Tempo comparabile con quello della somma.

Operazioni codificate in modo specifico nell'ISA.

A.A. 2006-2007

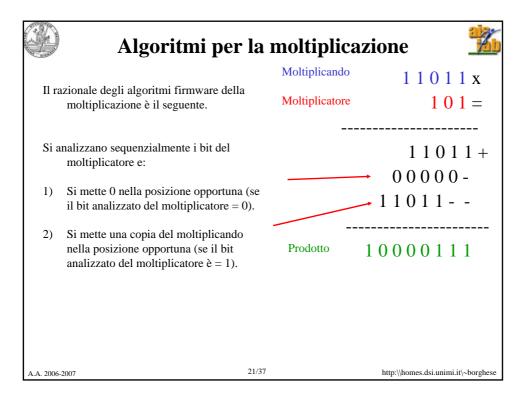

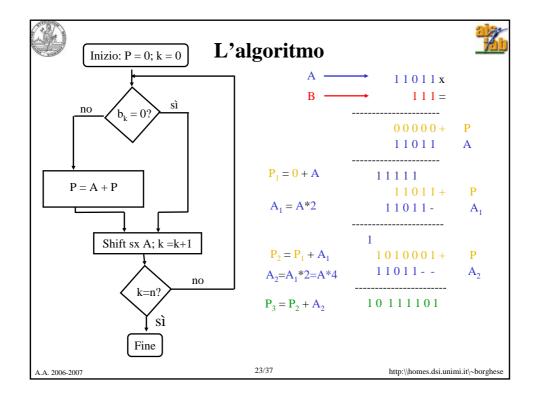

# L'approccio firmware

http:\\homes.dsi.unimi.it\~borghese

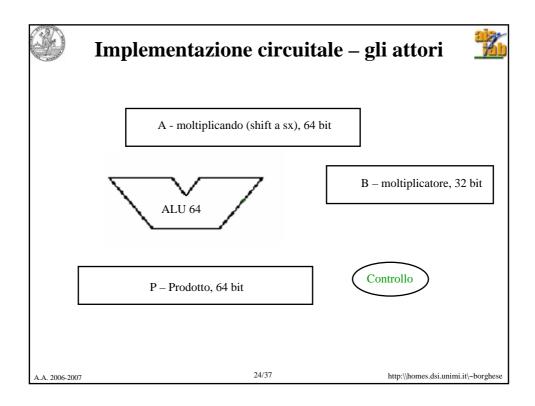

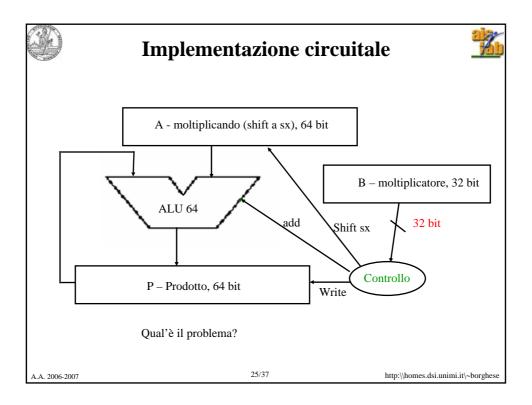

Nell'approccio firmware, viene inserita nella ALU una unità di controllo e dei registri. L'unità di controllo attiva opportunamente le unità aritmetiche ed il trasferimento da/verso i registri. Approccio "controllore-datapath".

Viene inserito un microcalcolatore dentro la ALU.

Il primo microprogramma era presente nell'IBM 360 (1964).

#### Esercizi

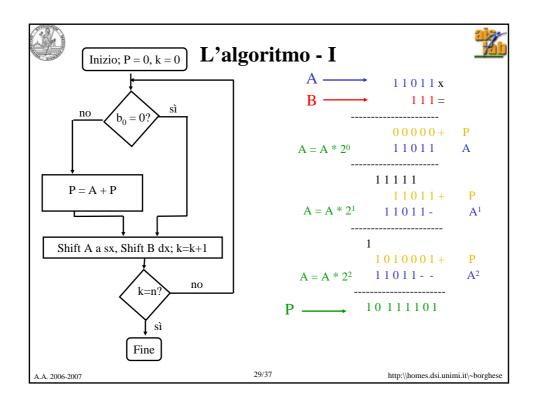

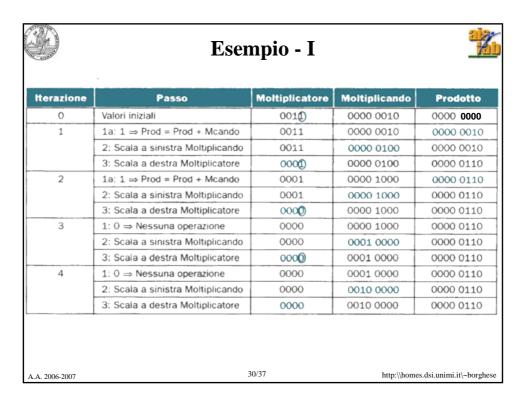

Costruire il circuito HW che esegui la moltiplicazione 7 x 9 in base 2.

Eseguire la stessa moltiplicazione secondo l'algoritmo visto, indicando passo per passo il contenuto dei 3 componenti: A che contiene il moltiplicando, B che contiene il moltiplicatore e P che contiene somme parziali ed il risultato finale.

#### Sommario

http:\\homes.dsi.unimi.it\~borghese

Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A.A. 2006-2007 27/

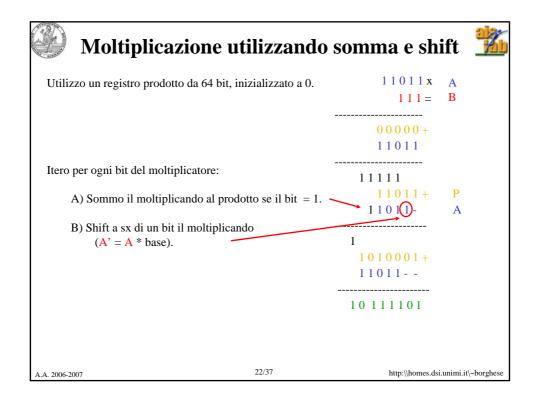

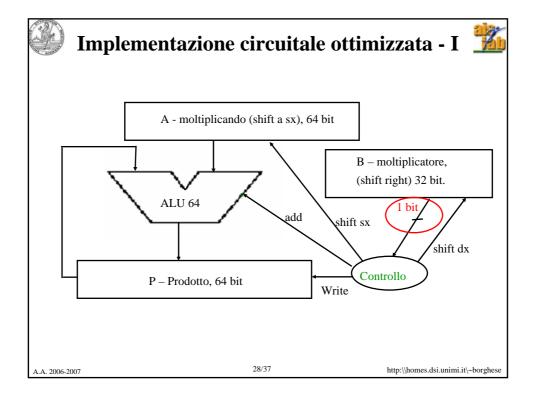

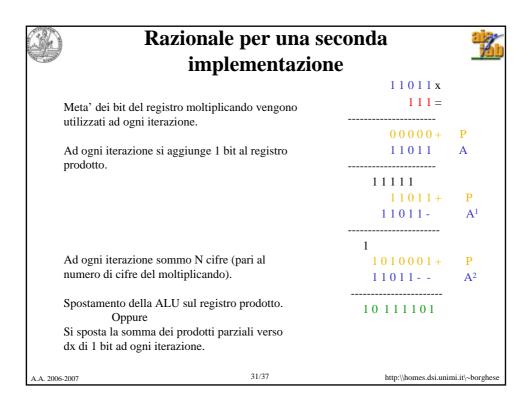

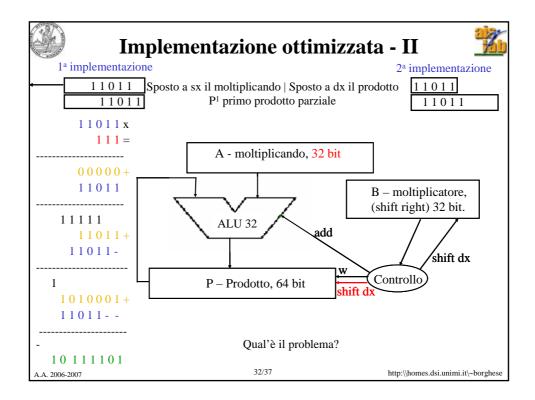

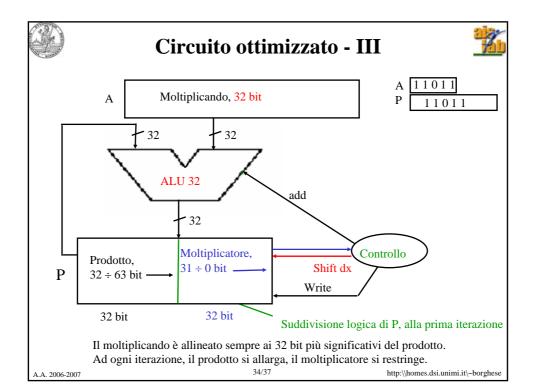

### Razionale dell'implementazione - III

Il numero di bit del registro prodotto corrente (somma dei prodotti parziali) più il numero di bit da esaminare nel registro moltiplicando rimane costante ad ogni iterazione (pari a 64 bit).

Si può perciò eliminare il registro moltiplicando.

A.A. 2006-2007 33/37 http:\\homes.dsi.unimi.it\~borghese

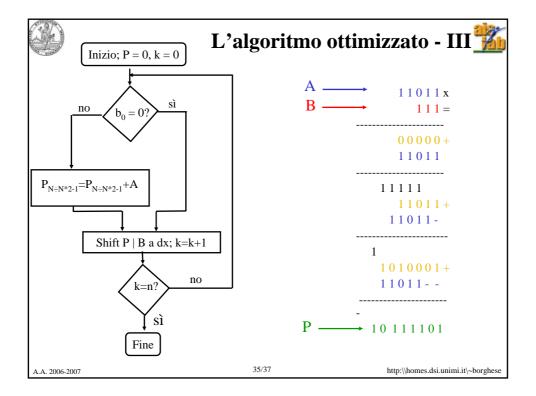

# Esempio di esecuzione dell'algoritmo ottimizzato - III

| Iterazione | Passo                        | Moltiplicando | Prodotto  |

|------------|------------------------------|---------------|-----------|

| 0          | Valori iniziali              | 0010          | 0000 0011 |

| 1          | 1a: 1 ⇒ Prod = Prod + Mcando | 0010          | 0010 0011 |

|            | 2: Scala a destra Prodotto   | 0010          | 0001 0000 |

| 2          | 1a: 1 ⇒ Prod = Prod + Mcando | 0010          | 0011 0001 |

|            | 2: Scala a destra Prodotto   | 0010          | 0001 1000 |

| 3          | 1: 0 ⇒ Nessuna operazione    | 0010          | 0001 1000 |

|            | 2: Scala a destra Prodotto   | 0010          | 0000 1100 |

| 4          | 1: 0 ⇒ Nessuna operazione    | 0010          | 0000 1100 |

|            | 2: Scala a destra Prodotto   | 0010          | 0000 0110 |

Il moltiplicando è allineato (e sommato) ai bit più significativi del prodotto.

A.A. 2006-2007

# Sommario

Problemi dei sommatori

Sommatori ad anticipazione di riporto

I problemi del moltiplicatore firmware

Ottimizzazione dei moltiplicatori firmware

A. 2006-2007

$http: \hspace{-0.05cm} \verb|\| homes.dsi.unimi.it| \hspace{-0.05cm} \sim borghese$