## Architettura degli Elaboratori Laurea Triennale in Comunicazione Digitale

## I prova in itinere - 22 maggio 2013

Compito **B**

| Cognome, nome: | Matricola: |

|----------------|------------|

|                |            |

- **1.** [2] Data la base  $B = \{ \Upsilon, \Xi, \Pi, \mathfrak{D}, \mathfrak{A}, \mathfrak{M}, \mathfrak{A} \}$  si converta il numero  $\mathfrak{A} \Pi \mathfrak{A}$  in base 10.

- 2. [1] Si completi la seguente tabella, supponendo di stare utilizzando la notazione in complemento a due per rappresentare numeri negativi.

| Decimale    | Binario | esadecimale |

|-------------|---------|-------------|

| 2 551111611 |         | 0×DECA      |

- 3. [2] A quale numero corrisponde la parola 0xBEC80000, secondo lo standard IEEE-754, singola precisione?

- **4.** [3] Si dimostri con passaggi algebrici l'espressione logica: a+ab+abc=a+b . Si scriva inoltre la sua espressione duale.

- 5. [5] Si disegni lo schema circuitale interno di una ALU a 4 bit in grado di fare somma e sottrazione. Si disegni sia lo schema circuitale interno di un modulo ALU elementare che lo schema a blocchi generale. Si calcoli il cammino critico e lo si evidenzi sullo schema.

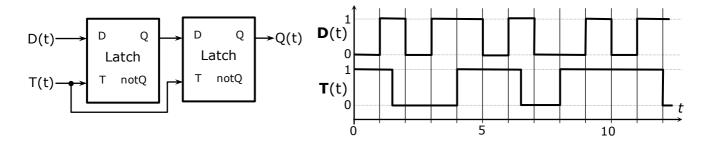

- 6. [4] Si disegni lo schema circuitale interno di un latch tipo D. Considerando il circuito in figura, si tracci nel grafico l'andamento dell'uscita Q(t).

- **7.** [5] Si progetti un circuito caratterizzato da 4 bit di ingresso  $(a_3 a_2 a_1 a_0)$  che rappresentano un numero N intero con segno (in complemento a 2), e da un'uscita Y che vale '1' se e solo se N è dispari quando è negativo e multiplo di 3 quando è positivo.

- a) Determinare la tabella di verità della funzione logica di uscita;

- b) scrivere la funzione nella forma canonica più adatta;

- c) semplificarla mediante mappa di Karnaugh;

- d) semplificarla ulteriormente, se possibile, mediante passaggi algebrici;

- e) disegnare lo schema circuitale corrispondente.

- 8. [8] Si sintetizzi una macchina a stati finiti (di Moore) caratterizzata da una linea d'ingresso I che viene osservata ogni secondo, e da una linea di uscita Y. La macchina funziona così: se l'ingresso è rimasto a '1' durante gli ultimi 2 secondi, l'uscita Y cambia di valore. Si considerino inizialmente sia l'ingresso che l'uscita a '0'. Si determinino STG, STT, STT codificata e struttura circuitale del sistema completo, non trascurando il clock ed avendo cura di semplificare il più possibile le funzioni prima di tradurle in circuito.