## Architettura degli Elaboratori e delle Reti

Turno 2 - Prof. Federico PEDERSINI

Università degli Studi di Milano Dip. Scienze dell'Informazione

## Appello del: 19 luglio 2005

Cognome, nome: Matricola:

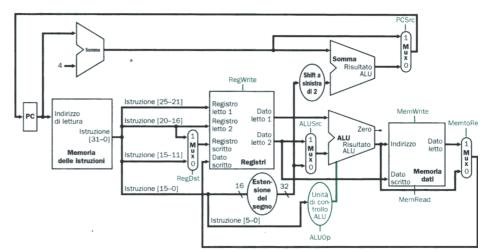

1. [8] Volendo rendere la CPU in figura in grado di eseguire le seguenti istruzioni (in formato MIPS):

```

add (tipo R, opcode: 0),

lw (tipo I, opcode: 35),

bne (tipo I, opcode: 5),

j (tipo J, opcode: 2),

progettare l'unità di

controllo e modificare,

se e dove necessario, la

struttura della CPU.

```

- **2.** [2] Disegnare lo schema circuitale di un flip-flop di tipo DT e descriverne il comportamento nei confronti dei fronti di salita e discesa all'ingresso T.

- **3.** [6] Si consideri un calcolatore con capacità di indirizzamento di memoria di 16 MByte ed ampiezza del bus dati di 8 bit. Si progetti, per tale sistema, una cache 2-associativa di capacità C = 8 kByte con linee di 16 parole. Dimensionare e disegnare lo schema della cache, mettendo in evidenza come i campi dell'indirizzo di memoria controllino il resto del circuito. Indicare inoltre in che posizione viene scritta la parola all'indirizzo 0x80F.

- **4.** [8] Si sintetizzi una macchina a stati finiti di Moore (rappresentando STG, STT e struttura circuitale) che fornisce in uscita "1" ogni qualvolta gli ultimi 5 bit in ingresso soano stati "11011", e "0" altrimenti.

- **5.** [6] Si traduca in linguaggio Assembly la seguente procedura recursiva (traducendo le eventuali pseudo-istruzioni):

- **6.** [2] Una CPU viene riprogettata dotata di una nuova ALU, mediante la quale le operazioni logico-aritmetiche richiedono un quinto del tempo prima necessario. Calcolare quanto deve essere la percentuale di tempo dedicata ad operazioni logica-aritmetiche, per la quale la velocità globale del sistema risulta raddoppiata.

- **7.** [3] Calcolare la distanza minima, la capacità di rivelazione e di correzione di un codice di correzione errori nel quale, per ogni coppia di bit in ingresso, viene aggiunto un terzo bit uguale al primo dei due.