## Architettura degli Elaboratori e delle Reti Turno 2 – Prof. Federico PEDERSINI

## II Compitino in itinere - 18 giugno 2009

Cognome, nome:

Matricola:

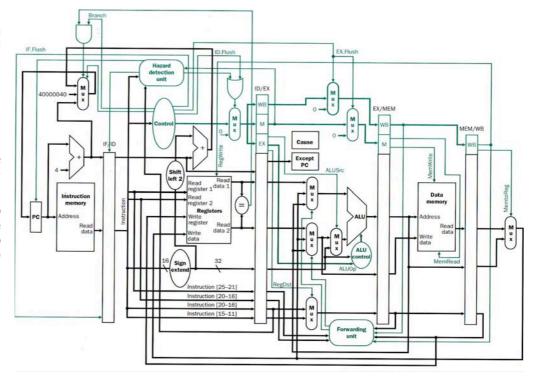

**1.** [6] Si consideri la CPU raffigurata a lato, la quale stia eseguendo il seguente codice:

0x100: add \$1, \$2, \$3 lw \$4, 20(\$1) addi \$5, \$4, 1 lw \$6, 0(\$5) sw \$7, 0(\$6)

Identificare e descrivere gli eventuali casi di criticità nel codice suindicato.

Determinare il contenuto dei registri ID/EX e EX/MEM (in uscita) dopo **8 cicli di clock** dall'inizio della prima istruzione.

- **2.** [4] Elencare e descrivere i criteri più comuni utilizzati nelle memorie cache a più vie per la scelta del banco in cui scrivere un nuovo blocco.

- **3.** [6] Un processore caratterizzato da uno spazio di indirizzamento della memoria principale di 64 GByte e da un bus dati di 64 bit viene dotato di una memoria cache associativa a 4 vie, di capacità totale C = 8 MByte e con linee di 16 parole. Dimensionare la cache, evidenziando le dimensioni di tutti i campi e disegnare lo schema dettagliato di tale memoria. Mostrare inoltre dove viene memorizzato, nella cache, il byte di memoria situato all' indirizzo:  $A = 2^{24} + 2^{18} + 2^{12} + 2^{8} + 15$ , evidenziando i valori di byte offset, word offset, index e tag.

- **4.** [4] Disegnare lo schema circuitale di una cella di memoria dinamica. Descrivere il meccanismo di lettura e quello di scrittura di un bit. Spiegare la funzione dei segnali RAS e CAS.

- **5.** [5] Si vogliono incrementare le prestazioni di un calcolatore mediante l'introduzione di una memoria cache (di cui il calcolatore è originariamente sprovvisto). Il tempo complessivo di lettura/scrittura in cache è di 1.25 nsec, mentre per la memoria principale occorrono 10 nsec.

- a) Di quanto aumenta la velocità del calcolatore in caso di miss-rate = 10%?

- b) Con che valore di miss-rate si ottiene un aumento di velocità del calcolatore di 5 volte?

- c) Mantenendo invece fisso il miss-rate a 10%, quanto dovrebbe valere il tempo di lettura/scrittura della memoria cache, per ottenere un incremento di velocità del calcolatore di 5 volte?

- **6.** [4] Si consideri un codice di controllo errori che, semplicemente, replica ogni coppia di bit per altre due volte. Elencare le parole di codice valide, calcolare il costo del codice e la sua capacità di correzione.

- **7.** [4] Spiegare in che modo nel protocollo di trasporto TCP sia possibile effettuare il controllo di flusso, cioè l'adattamento della velocità di trasmissione del mittente alla capacità di "assorbire" i dati da parte del destinatario.

- 8. [3] Individuare e descrivere le principali differenze tra l'architettura MIPS e la Intel IA-32.