## Architettura degli Elaboratori e delle Reti Turno 2 – Prof. Federico PEDERSINI

## I Compitino in itinere - 7 maggio 2007

Cognome, nome:

Matricola:

**1.**[1.5] Si completi la seguente tabella, supponendo che si stia utilizzando la rappresentazione in complemento a 2 per i numeri negativi, su 8 bit:

| Base 10 | Base 2 | Base 16 |

|---------|--------|---------|

|         |        | AE      |

2. [1.5] Si rappresenti il seguente numero in formato IEEE-754 – singola precisione:

```

-10,625

```

- **3.** [4] Si progetti un circuito in grado di calcolare la differenza tra due numeri di 8 bit, utilizzando circuiti sommatori (HA, FA) sfruttando le proprietà della rappresentazione in complemento a 2 per numeri negativi).

- **4.** [3] Si dimostri che:  $ab \oplus cd = ab\overline{c} + ab\overline{d} + \overline{acd} + \overline{bcd}$  utilizzando le proprietà dell'algebra booleana.

- **5.** [11] Si sintetizzi una macchina a stati finiti (di Moore) che realizza un contatore modulo 4 così strutturato:

- L'ingresso è costituito da una linea di 2 bit che rappresenta il valore di cui incrementare il contatore, rappresentato in modalità "modulo e segno" (1 bit di segno + 1 bit di valore).

- L'uscita è costituita da 4 linee, che rappresentano i 4 valori assumibili dal contatore: ciascuna uscita va a "1" solo quando il contatore contiene il valore da essa rappresentato.

- Allo scadere di ogni secondo, il contatore incrementa il proprio valore della quantità pari al valore presente sugli ingressi (considerando il segno).

- Si determinino STG, STT, STT codificata e struttura circuitale del sistema completo.

- 6. [7] Si traduca in linguaggio <u>Assembly MIPS nativo</u> la seguente procedura C. Il parametro vada posto in \$a0 ed il risultato in \$v0; (N.B. si consideri la divisione fra interi, trascurando il resto).

```

int log2( int x )

{

if( x < 2 )

return( 0 );

else

return( 1 + log2(x/2) );

}</pre>

```

7. [6] Si traducano le seguenti pseudoistruzioni: a) in Assembly MIPS nativo e b) in linguaggio macchina MIPS (specificando dimensione in bit e valore dei campi di ogni istruzione).

li \$s1, 2<sup>24</sup> div \$t0, \$t1, \$t2 blti \$s0, 5, -16

Convenzione registri MIPS:

| 0     | \$zero    |  |

|-------|-----------|--|

| 1     | \$at      |  |

| 2-3   | \$v0-\$v1 |  |

| 4-7   | \$a0-\$a3 |  |

| 8-15  | \$t0-\$t7 |  |

| 16-23 | \$s0-\$s7 |  |

| 24-25 | \$t8-\$t9 |

|-------|-----------|

| 26-27 | \$k0-\$k1 |

| 28    | \$gp      |

| 29    | \$sp      |

| 30    | \$s8      |

| 31    | \$ra      |

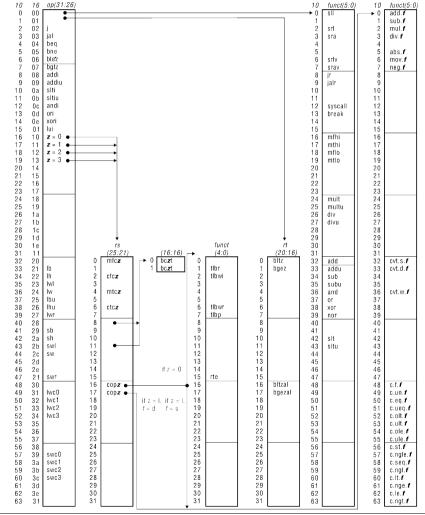

MIPS Instruction Set: