## Architettura degli Elaboratori 2

Laurea triennale in Informatica

Turno 2 – Prof. Federico PEDERSINI

Appello del 11 luglio 2018

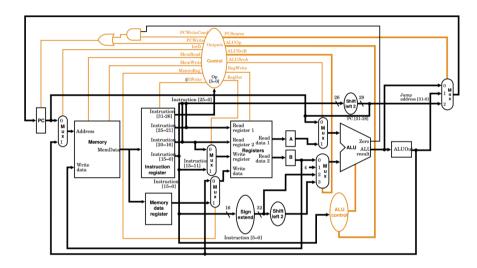

[5] Considerando la CPU in figura, determinare il contenuto dei registri PC, IR, MDR e ALUout, per ogni ciclo di clock necessario ad eseguire il frammento di codice a lato. 0xAFC: addi \$5,\$0, -7 sw \$5, 32(\$0) lw \$6, 32(\$0) beg \$5, \$6, 40

(Opcode addi=8, sw=44, lw=36, beq=4)

- 2. [5] In una CPU con frequenza di clock 1 GHz e bus dati di 32 bit, una periferica trasferisce informazioni mediante DMA, trasferendo blocchi di 10.000 byte per volta in modo sincrono sul bus (1 parola/ciclo di clock). Supponendo che siano necessari 1500 cicli di clock per l'inizializzazione e altri 500 per la terminazione di ogni blocco DMA, calcolare:

- a) la velocità di trasferimento periferica/memoria ottenibile con un'occupazione percentuale di tempo di CPU pari a 1%.

- b) la percentuale di tempo di CPU dedicata al trasferimento dati dalla stessa periferica, se si utilizzassero chiamate di interrupt anziché il DMA, supponendo che ogni chiamata di interrupt richieda 150 cicli di clock e trasferisca 16 parole alla volta.

- **3.** [4] Descrivere il funzionamento dell'unità di rivelazione delle criticità ("hazard detection unit") della CPU pipeline MIPS, identificando tutti gli ingressi e le uscite dell'unità e definendo esattamente il suo algoritmo di funzionamento.

- **4.** [5] Un processore caratterizzato da uno spazio di memoria indirizzabile di 512 MByte e un bus dati di 64 bit viene dotato di una memoria a mappatura diretta di capacità totale di 256 kByte e linee di 16 parole.

- a) Disegnare lo schema circuitale dettagliato di tale memoria;

- b) calcolare il numero di bit necessari per ogni linea (includendo tutti i campi);

- c) determinare l'indirizzo di memoria principale (in esadecimale) corrispondente a: byte offset=3, word offset=5, index=20 e tag=9.

- **5.** [5] Disegnare la struttura circuitale di una cella di memoria RAM dinamica e spiegare come avviene la scrittura di un "1" nella cella. Disegnale la struttura circuitale generale di un chip di memoria dinamica di 64M x 1 bit e calcolare il tempo massimo di refresh ammesso da tale chip, se il tempo di scarica delle celle è di 102,4 millisecondi.

- **6.** [6] Descrivere il funzionamento di un sistema di memoria virtuale, rappresentandone in dettaglio lo schema funzionale. Si consideri un elaboratore che dispone di una memoria fisica di 64 MB e gestisce uno spazio di memoria virtuale di 1 GB. Considerato che la dimensione delle pagine è di 4 kB e l'ampiezza di parola è di 32 bit, calcolare:

- a) la dimensione della Page Table (supponendo che ogni linea di page table occupi una parola di memoria);

- b) l'indirizzo virtuale (in esadecimale) della <u>prima</u> parola della <u>quinta</u> pagina.

System calls

| System cans  |                  |           |                   |  |  |  |  |

|--------------|------------------|-----------|-------------------|--|--|--|--|

|              | codice<br>(\$v0) | argomenti | risultato         |  |  |  |  |

| print_int    | 1                | \$a0      |                   |  |  |  |  |

| print_float  | 2                | \$f12     |                   |  |  |  |  |

| print_double | 3                | \$f12     |                   |  |  |  |  |

| print_string | 4                | \$a0      |                   |  |  |  |  |

| read_int     | 5                |           | \$ <del>v</del> 0 |  |  |  |  |

| read_float   | 6                |           | \$£0              |  |  |  |  |

| read_double  | 7                |           | \$£0              |  |  |  |  |

| read_string  | 8                | \$a0,\$a1 |                   |  |  |  |  |

| sbrk         | 9                | \$a0      | \$ <del>v</del> 0 |  |  |  |  |

| exit         | 10               |           |                   |  |  |  |  |

Registri MIPS

| 0     | zero  | 24-<br>25 | t8-t9 |

|-------|-------|-----------|-------|

|       |       |           |       |

| 1     | at    | 26-       | k0-k1 |

|       |       | 26-<br>27 |       |

| 2-3   | v0-v1 | 28        | Gp    |

| 4-7   | a0-a3 | 29        | Sp    |

| 8-15  | t0-t7 | 30        | s8    |

| 16-23 | s0-s7 | 31        | Ra    |