Turno 2 - Prof. Federico PEDERSINI Appello del 21 gennaio 2015

- 1. [2] Scrivere in formato esadecimale la codifica IEEE-754 (singola precisione) del numero: **-2**<sup>-131</sup>.

- **2.** [3] Enunciare e dimostrare le due leggi dell'assorbimento, in entrambe le forme duali.

- 3. [6] Si progetti un circuito caratterizzato da quattro linee d'ingresso A,B,C,D e da un'uscita U che vale '1' se e solo se A+BC+D=0 .

- a) Determinare la tabella di verità di U; b) esprimerla nella forma canonica più adatta; c) semplificarla mediante mappe di Karnaugh; d) semplificarla ulteriormente, se possibile, mediante semplificazioni algebriche; e) disegnare il circuito.

- **4.** [4] Si disegni lo schema di un circuito che calcola la differenza tra due numeri binari con segno A e B di 4 bit. Evidenziare sullo schema il cammino critico e determinarne il valore.

- 5. [8] Si sintetizzi una macchina a stati finiti di Moore sincrona caratterizzata da una linea d'ingresso I e da una linea di uscita Q. Ogni qualvolta sulla linea I si presenta un fronte di discesa seguito immediatamente da un fronte di salita, l'uscita cambia di valore. All'accensione, si suppongano I e Q a 0. Si determinino: STG, STT, STT codificata e struttura circuitale del sistema completo, gestendo il segnale di clock ed avendo cura di semplificare il più possibile le funzioni prima di tradurle in circuito.

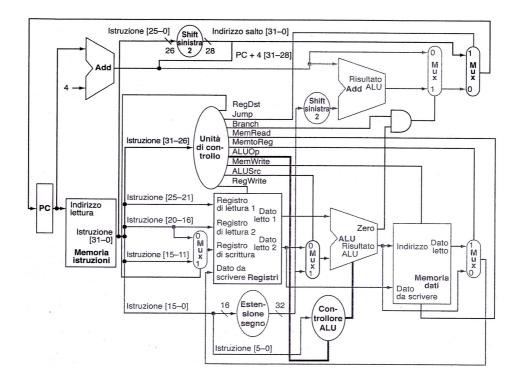

- **6.** [8] Determinare, nella sequente CPU: a) i valori in ingresso e in uscita da: ogni ALU, dai multiplexer relativi ai salti e dal Register File; b) i valori di ogni segnale di controllo, supponendo che la CPU abbia eseguito le istruzioni a lato e stia in questo momento eseguendo l'ultima istruzione.

## 0x00000AC8:

ori \$8, \$0, +15

and \$9, \$8, \$0

beq \$8, \$9, -16

OpCodes: ori=13; beq=4; and=0 (funct=32).