## Architettura degli Elaboratori e delle Reti

Turno 2 - Prof. Federico PEDERSINI

## I Compitino in itinere – 5 maggio 2008 – Compito **B**

Cognome, nome:

Matricola:

**1.** [1.5] Si completi la seguente tabella, supponendo che si stia utilizzando la rappresentazione in complemento a 2 per i numeri negativi, su 16 bit:

| Base 10 | Base 2 (su 16 bit) | Base 16 |

|---------|--------------------|---------|

|         |                    | FE70    |

2. [1.5] Si rappresenti il seguente numero in formato IEEE-754 – singola precisione:

| -11,5625 | ,5625 |  |  |  |  |  |  |  |  |

|----------|-------|--|--|--|--|--|--|--|--|

|----------|-------|--|--|--|--|--|--|--|--|

- **3.** [7] Si progetti un circuito "comparatore", caratterizzato da due linee in ingresso, **A** e **B**, di 2 bit ciascuna, e da un bit di uscita **c**, che vale: "1" se il numero binario rappresentato all'ingresso A è maggiore di quello all'ingresso B; "0" in caso contrario.

- a) Determinare la tabella di verità della funzione logica di uscita;

- b) scrivere la funzione nella forma canonica più adatta;

- c) semplificarla mediante mappa di Karnaugh;

- d) semplificarla ulteriormente, se possibile, mediante passaggi algebrici;

- **4.** [10] Si sintetizzi una macchina a stati finiti (di Moore) che realizza un contatore modulo 4, che funziona come segue:

Il valore dei 2 ingressi viene letto ad ogni centesimo di secondo.

La macchina presenta 2 ingressi, chiamati "+" e "-". Quando l'ingresso "+" vale "1" il contatore viene incrementato di 1, mentre quando l'ingresso "-" vale "1", il contatore viene decrementato di 1. Con entrambi gli ingressi a "0", il valore del contatore rimane invariato. Si escluda, per semplicità, che entrambi gli ingressi possano valere "1".

L'uscita è costituita da 4 linee, che rappresentano i 4 valori assumibili dal contatore: ciascuna uscita va a "1" solo quando il contatore contiene il valore da essa rappresentato.

Si determinino STG, STT, STT codificata e struttura circuitale del sistema completo, avendo cura di semplificare il più possibile le funzioni prima di tradurle in circuito.

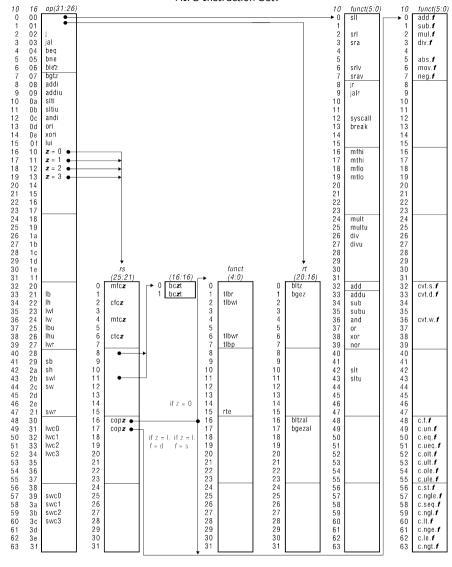

- **5.** [6] Si descrivano i modi di indirizzamento utilizzati nelle seguenti istruzioni MIPS, spiegando, per ognuno, come vengono implementati circuitalmente: **addi**, **j**, **sw**

- **6.** [6] Si traducano le seguenti pseudoistruzioni: **a)** in Assembly MIPS nativo e **b)** in linguaggio macchina MIPS (specificando dimensione in bit e valore dei campi di ogni istruzione).

li \$8, 128<sup>3</sup>

**lw \$15 \$16 (\$17)** # offset contained in register 16

**blei \$18**, **1**, **-24** # (branch on less or equal than - immediate)

## MIPS Instruction Set: