Laurea triennale in Informatica Turno 2 – Prof. Federico PEDERSINI

## Appello del 21 giugno 2016

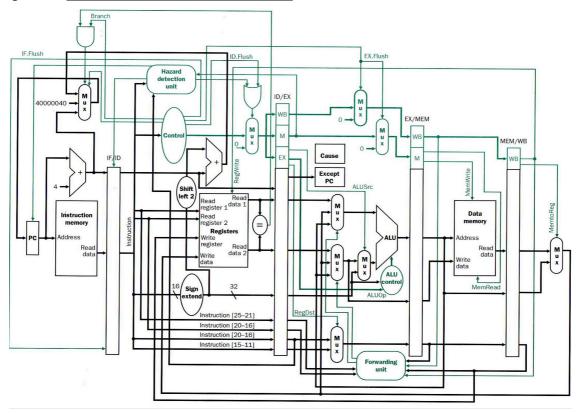

[8] Si consideri la CPU seguente che esegue il codice a lato.

a) Identificare gli eventuali casi di criticità nel codice e descrivere come vengono gestiti dalla CPU (si noti che è presente il circuito per l'anticipazione dei salti condizionati);

b) determinare il contenuto del registro **ID/EX dopo 8 cicli di clock** dall'inizio della prima istruzione;

c) determinare quanti cicli di clock sono necessari per arrivare ad eseguire la fase di fetch dell'ultima istruzione.

0xF80: lw \$2, 0(\$1)

add \$3, \$2, \$0

beq \$2, \$3, +8

lw \$5, 0(\$3)

add \$6, \$5, \$5

sw \$6, 0(\$10)

- 2. [5] Un processore caratterizzato da uno spazio di memoria indirizzabile di 4 MByte e un bus dati di 8 bit viene dotato di una memoria a mappatura diretta di capacità di 64 kByte e linee di 16 parole. a) Calcolare esattamente <u>quanti bit</u> di memoria contiene la cache (considerando anche quelli per memorizzare il bit di validità e il campo tag); b) calcolare il valore (in <u>esadecimale</u>) di: byte offset, word offset, index e tag corrispondenti all' indirizzo di memoria principale: 0x12345.

- **3.** [5] Disegnare la struttura circuitale di una cella di memoria dinamica e spiegarne il funzionamento. Disegnare quindi la struttura modulare di un chip di memoria dinamica da 16 Mbit (16 Mcelle da 1 bit) e determinare la minima frequenza di refresh per un tempo di scarica dei condensatori di 81,92 ms.

- **4.** [4] Si consideri una tecnica di controllo errori in memoria che consiste nel replicare, per ogni coppia di bit, la coppia stessa, negata. Si definiscano le parole valide di tale codice, si calcoli la distanza minima del codice e le sue capacità di rivelazione e di correzione.

- **5.** [5] Spiegare come funziona la memoria virtuale, descrivendo, anche mediante uno schema circuitale, come funziona l'accesso alla memoria attraverso l'uso della page table e del page table register mostrando esplicitamente come avviene la conversione da indirizzi virtuali a indirizzi fisici. Si spieghi inoltre il ruolo e il funzionamento del Transition Look-aside Buffer

- **6.** [3] Si illustrino i modi comunemente utilizzati in una chiamata di servizio all'interrupt per fornire le informazioni relative al tipo di evento che lo ha generato.