## Architettura degli Elaboratori e delle Reti

# Architetture sincrone e asincrone Sintesi di circuiti sequenziali

Federico Pedersini

Dipartimento di Informatica Università degli Studi di Milano

A.A. 2017/18 © F. Pedersini – DI, UniMI L 8 – 1

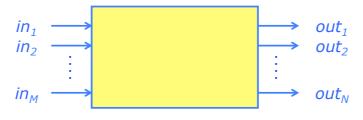

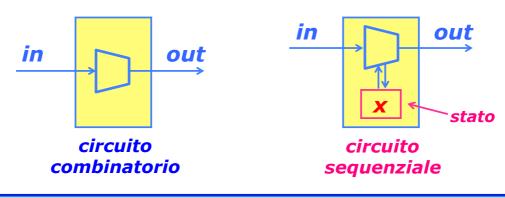

## Circuiti combinatori

#### Circuiti combinatori = circuiti senza memoria:

Le uscite al tempo t dipendono unicamente dagli ingressi al tempo t

$$out_i = f_i(in_1, in_2, \dots, in_M)$$

,  $i = 1 \dots N$

- Ogni uscita out; è una funzione logica degli ingressi in; ... in<sub>M</sub>

- > Indipendenza dal tempo

- È impossibile modificare la "storia" del circuito → non c'è memoria

Circuito combinatorio

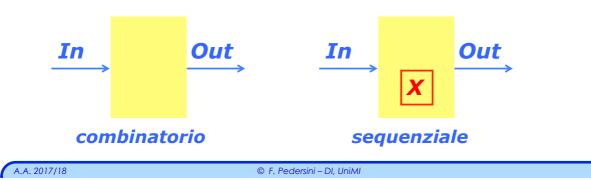

## Circuiti sequenziali

- ❖ Circuiti combinatori = circuiti senza memoria

- > Gli output al tempo t dipendono unicamente dagli input al tempo t

Out =

$$f(In)$$

- Per consentire ad un dispositivo di mantenere le informazioni, sono necessari circuiti con memoria

- Circuiti sequenziali = circuiti con memoria (stato)

- > La memoria contiene lo stato (X) del sistema:

$$Out = f(In, X)$$

# Circuiti sequenziali

L8-3

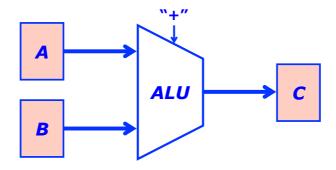

#### Circuiti sequenziali, o con memoria

- Sono necessari perché...

- In un sistema di elaborazione di informazioni è necessario poter conservare per un certo tempo le informazioni

$$C = A + B;$$

...

$C = C + 1;$

➤ "conservare per un certo tempo" → MEMORIZZARE

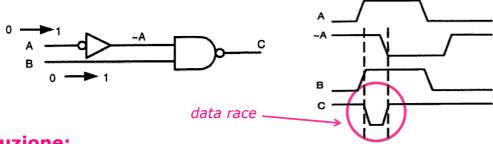

## Data races

#### Sono necessari perché...

al crescere della complessità dei circuiti combinatori, si verificano fenomeni critici:

- "Data races": transizioni spurie (glitch) su un segnale che deve rimanere costante

- → C'è un *limite alla complessità* dei circuiti combinatori!

#### **Soluzione:**

- spezzo il circuito in SEZIONI

- inserisco tra le sezioni delle **BARRIERE** al segnale, che "APRO" solo quando i segnali sono *STABILI*.

A.A. 2017/18 © F. Pedersini – DI, UniMI L 8 – 5

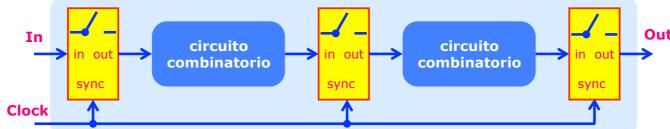

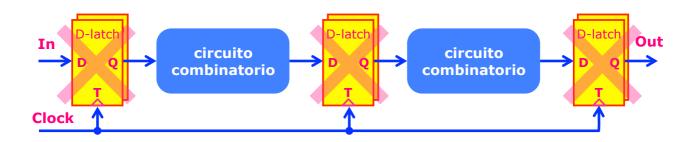

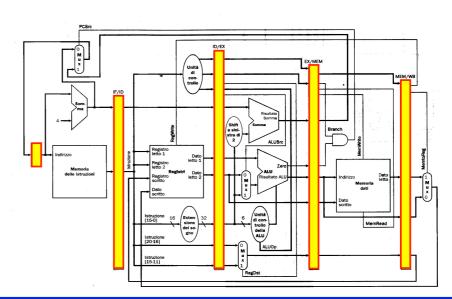

# Struttura di architetture sincrone

#### **Cancello** → Circuito combinatorio → Cancello

- Sincronizzazione: la logica combinatoria deve terminare la propria commutazione in tempo utile

- Dimensionamento del periodo di clock T:

- > La commutazione del clock deve avvenire **dopo** che la logica combinatoria abbia terminato tutte le commutazioni

- > Il tempo necessario alla logica combinatoria per commutare dipende dal cammino critico

## Perchè esiste il "clock" ?

#### Dove il "cancello" viene inserito, si *sincronizza* l'attività di elaborazione

Altrimenti i cammini critici renderebbero il funzionamento del circuito sempre più casuale.

#### "cancelli" = barriere di sincronizzazione tra circuiti

- > Memorizzano l'ingresso ad un certo istante

- → dispositivi di memorizzazione: registri

- > Lo mantengono stabile in uscita, per un certo periodo

- → orologio in comune: **segnale di clock**

orologio comune

- → circuiti sincroni

- presenza di <u>registri</u>  $\rightarrow$  **circuiti sequenziali** (con memoria)

A.A. 2017/18

© F. Pedersini – DI, UniMI

L8-7

## Circuiti sincroni e asincroni

#### Architettura sincrona:

l'elaborazione e propagazione dei segnali è scandita da un orologio comune a tutto il circuito (clock)

- Il Clock regola l'attività dei "cancelli"

- Il circuito ha il tempo di stabilizzarsi (transitori critici) fino al successivo impulso di Clock

#### \* Architettura asincrona:

l'elaborazione e propagazione dei segnali avviene in modo incontrollato, secondo le velocità di reazione dei circuiti

- > Non ci sono cancelli

- Non devo mai aspettare l'impulso di clock → massima velocità

#### Progettazione sincrona

il controllo dei transitori/cammini critici è limitato alla parte di circuito tra due cancelli (porte di sincronizzazione)

#### Progettazione asincrona

> Devo progettare il circuito in modo che nessun transitorio/cammino critico causi problemi → analisi di tutti i transitori critici possibili.

#### Eccezioni: TRANSPUTER (INMOS, UK)

- > Architettura di calcolatore con CPU asincrona

- ➤ Complessità enorme, sia di progettazione che di programmazione → progetto abbandonato.

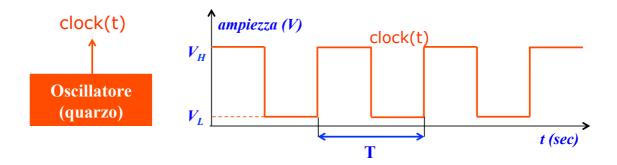

## Clock

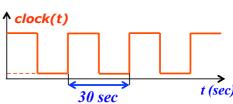

**Periodo**: **T** [s] durata di 1 ciclo (secondi) **Frequenza**: f [Hz]=[s<sup>-1</sup>] numero di cicli al secondo

$$T = 1/f$$

Tempo di salita e discesa trascurabile, rispetto al periodo T.

A.A. 2017/18 © F. Pedersini – DI, UniMI L8 – 9

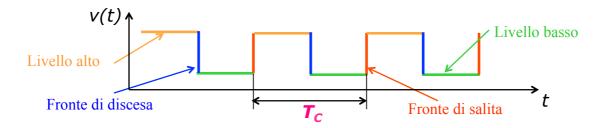

## Utilizzo del clock

- Architettura sensibile ai livelli:

- ➤ Le <u>variazioni di stato</u> avvengono quando il clock è alto (basso). La parte bassa (alta) del ciclo di clock permette la <u>propagazione tra sottocircuiti</u>, così che i segnali si siano stabilizzati quando il clock cambia livello.

- \* Architettura sensibile ai fronti:

- ➤ Le variazioni di stato avvengono in corrispondenza di un fronte di clock (salita o discesa).

## Circuiti sequenziali

- Circuiti combinatori = circuiti senza memoria

- $\succ$  Gli output al tempo  $m{t}$  dipendono unicamente dagli input al tempo  $m{t}$

$$Out = f(In)$$

- > Per consentire ad un dispositivo di mantenere le informazioni, sono necessari circuiti con memoria

- ❖ Circuiti sequenziali = circuiti con memoria (stato)

- > La memoria contiene lo **stato (X)** del sistema:

$$Out = f(In, X)$$

A.A. 2017/18 © F. Pedersini – DI, UniMI L8 – 11

## Latch & Bistabili

- Elemento cardine dei circuiti sequenziali è lo stato

- > Lo stato riassume il funzionamento negli istanti precedenti e deve essere immagazzinato (memorizzato)

- Elemento base della memoria è il bistabile

- > dispositivo in grado di mantenere indefinitamente un valore in ingresso

- > Il suo valore di uscita coincide con lo stato

- \* Tipologie di bistabile

- > Bistabili non temporizzati (asincroni) / temporizzati (sincroni).

- ➤ Bistabili (sincroni) che commutano sul <u>livello</u> (latch) o sul <u>fronte</u> (flip-flop)

- ▶ Memoria: insieme di bistabili (bistabili → registri → memorie)

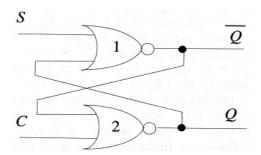

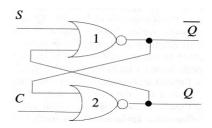

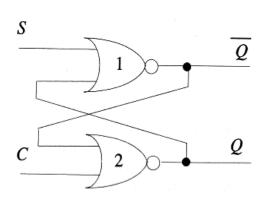

# Latch Set-Clear (SR) asincrono

Una coppia di porte NOR retroazionate può memorizzare un bit!

A.A. 2017/18

© F. Pedersini – DI, UniMI

L8 – 13

# Funzionamento del Latch SC (SR)

Latch Set-Reset (Set-Clear)

CQ $\overline{\varrho}$

- Funzionamento:

- C = 0,  $S \rightarrow 1$   $Q \rightarrow 1$   $(\sim Q \rightarrow 0)$  S = 0,  $C \rightarrow 1$   $Q \rightarrow 0$   $(\sim Q \rightarrow 1)$

- > Comportamenti anomali:

- > S = 1, C:  $0\rightarrow 1$  $Q = \sim Q = 0$  (anomalia)

A.A. 2017/18

© F. Pedersini – DI, UniMI

L8-14

## Tabella delle transizioni

- Un circuito sequenziale non si può rappresentare mediante una tabella di verità

- ❖ Per i circuiti sequenziali si definisce la tabella delle transizioni

Tabella delle transizioni:  $Q^* = f(Q, I) = f(Q, S, C)$

Q: valore dell'uscita attuale: stato correnteQ\*: uscita al tempo successivo: stato prossimo

$$Q^* = f(Q,I)$$

| <b>Q \ I</b> | SC = 00 | SC = 01 | SC = 11 | SC = 10 |

|--------------|---------|---------|---------|---------|

| 0            | 0       | 0       | X       | 1       |

| 1            | 1       | 0       | X       | 1       |

$$\uparrow_{Q^* = Q}$$

$\uparrow_{Clear/Reset}$

A.A. 2017/18 © F. Pedersini – DI, UniMI L 8 – 15

## Tabella delle transizioni

Tabella delle transizioni f:

$$Q^* = \boldsymbol{f}(I,Q) = \boldsymbol{f}(S,C,Q)$$

| SC<br>Q | SC=00 | SC=01 | SC=11 | SC=10 |

|---------|-------|-------|-------|-------|

| Q=0     | 0     | 0     | X     | 1     |

| Q=1     | 1     | 0     | X     | 1     |

Considerando lo stato Q come ingresso ottengo la <u>tabella delle verità</u> di Q\*:

$$Q^* = S + Q\overline{C}$$

| S | U | Q | Q* |

|---|---|---|----|

| 0 | 0 | 0 | 0  |

| 0 | 0 | 1 | 1  |

| 0 | 1 | 0 | 0  |

| 0 | 1 | 1 | 0  |

| 1 | 0 | 0 | 1  |

| 1 | 0 | 1 | 1  |

| 1 | 1 | 0 | X  |

| 1 | 1 | 1 | X  |

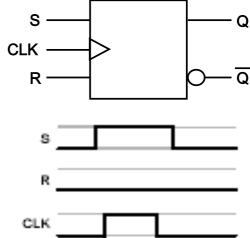

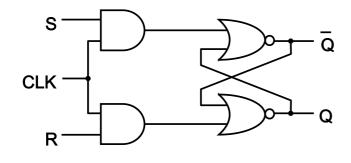

# Latch SR sincrono

#### Latch Set-Reset (SR) sincrono

#### Struttura: Latch SR + porte AND

tra il clock e gli ingressi.

Solo quando il <u>clock è alto</u> i "cancelli" (porte AND) fanno passare gli input → **LATCH**

CLK

Q

ZAT

A.A. 2017/18

© F. Pedersini – DI, UniMI

L8 – 17

# Sintesi della funzione logica

## Tabella delle transizioni: $Q^* = f(S,R,T,Q)$

| T | Q | S | R | Q* |

|---|---|---|---|----|

| 0 | 0 | 0 | 0 | 0  |

| 0 | 0 | 0 | 1 | 0  |

| 0 | 0 | 1 | 0 | 0  |

| 0 | 0 | 1 | 1 | 0  |

| 0 | 1 | 0 | 0 | 1  |

| 0 | 1 | 0 | 1 | 1  |

| 0 | 1 | 1 | 0 | 1  |

| 0 | 1 | 1 | 1 | 1  |

| 1 | 0 | 0 | 0 | 0  |

| 1 | 0 | 0 | 1 | 0  |

| 1 | 0 | 1 | 0 | 1  |

| 1 | 0 | 1 | 1 | X  |

| 1 | 1 | 0 | 0 | 1  |

| 1 | 1 | 0 | 1 | 0  |

| 1 | 1 | 1 | 0 | 1  |

| 1 | 1 | 1 | 1 | X  |

| TQ | SR = 00 | SR = 01 | SR = 11 | SR = 10 |

|----|---------|---------|---------|---------|

| 00 | 0       | 0       | 0       | 0       |

| 01 | 1       | 1       | 1       | 1       |

| 11 | 1       | 0       | X       | 1       |

| 10 | 0       | 0       | X       | 1       |

$$Q^* = \overline{T}Q + TQ\overline{R} + TS =$$

$$= \overline{T}Q + T(Q\overline{R} + S)$$

$$\stackrel{\text{clock alto}}{\text{clock basso}} \rightarrow Q^* = Q - R + S \text{ (bistabile)}$$

$$\stackrel{\text{clock alto}}{\text{clock basso}} \rightarrow Q^* = Q \text{ (status quo)}$$

# Analisi della funzione logica sintetizzata

## Latch Set-Reset (SR) sincrono

$$Q^* = \overline{T}Q + T(Q\overline{R} + S)$$

$$T = 1 \rightarrow Q^* = Q\overline{R} + S:$$

$$\begin{cases} \text{Set}: S = 1, R = 0 & Q^* = Q + 1 = 1 \\ \text{Reset}: S = 0, R = 1 & Q^* = 0 + 0 = 0 \end{cases}$$

$$T = 0 \rightarrow Q^* = Q$$

: "status quo"

A.A. 2017/18

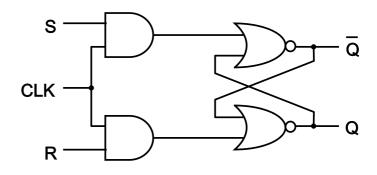

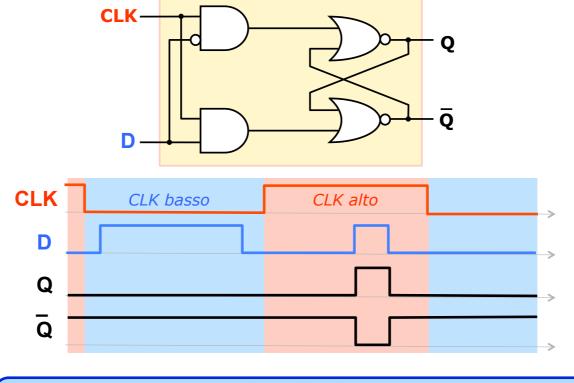

## Comportamento del Latch D

Latch SR un po' scomodo: 2 ingressi separati per memorizzare "0" o "1"

IDEA: piloto S e R con un solo ingresso: D

$$D = 1 \rightarrow S=1$$

, R=0 (Set)  $\rightarrow Q=1$

$D = 0 \rightarrow S=0$ , R=1 (Reset)  $\rightarrow Q=0$

$$D = 0 \rightarrow S=0, R=1 (Reset) \rightarrow Q=0$$

#### LATCH D:

#### Clock ALTO (CLK=1):

▶ L'uscita Q insegue l'ingresso D (con 3t<sub>p</sub> di ritardo)

#### Clock BASSO (CLK=0):

L'uscita Q rimane bloccata sull'ultimo valore assunto

A.A. 2017/18 L8 - 20

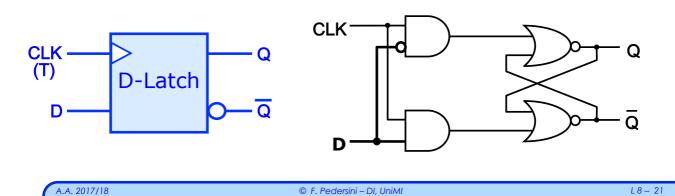

## Latch D sincrono

#### **LATCH D sincrono:**

Memorizza il valore presente all'ingresso dati quando il clock è alto, altrimenti (clock=0) si mantiene sul valore memorizzato

if

$$CLK = 1$$

then  $Q^*=D$  else  $Q^*=Q$

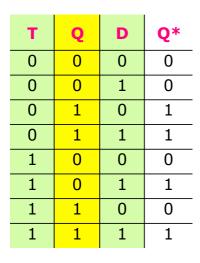

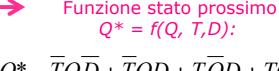

## La struttura del latch D

#### Tabella delle transizioni

Dalla tabella delle transizioni calcolo l'espressione logica della funzione stato prossimo Q\* = f(T,Q,D):

Tabella delle transizioni

$$Q^* = \overline{T}Q\overline{D} + \overline{T}QD + T\overline{Q}D + TQD =$$

$$= \overline{T}Q + TD$$

$$Clock T alto:$$

$$Q^* = D (input)$$

$$Clock T basso$$

$$Q^* = Q (status quo)$$

$$T = 1$$

$\rightarrow$   $Q^* = D$

$T = 0$   $\rightarrow$   $Q^* = Q$

A.A. 2017/18 © F. Pedersini – DI, UniMI L8 – 23

#### Latch: Bistabili level-sensitive

I latch sono dispositivi **trasparenti:** per tutto il tempo in cui il clock è a livello alto, il valore di D viene riportato in uscita

Clock = 1 → Q\*=D (uscita collegata all'ingresso)

Possono funzionare come "cancelli"?

**NO!** Nel momento in cui "apro" (T=1), i segnali possono attraversare **TUTTI gli stadi**.

Soluzione: "cancello doppio"

Quando apro in ingresso, l'uscita è chiusa, e viceversa.

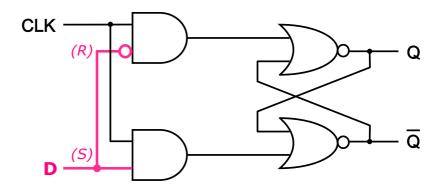

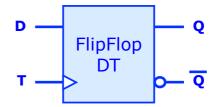

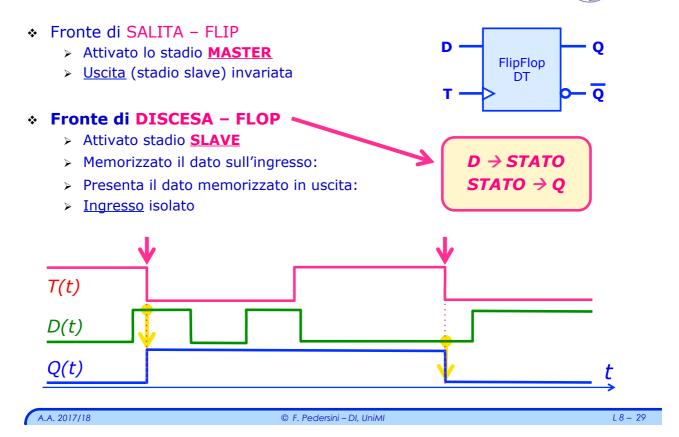

# Bistabili "edge sensitive": i Flip-Flop

**FLIP-FLOP**: bistabile <u>edge sensitive</u> (attivo sui fronti del clock):

lo stato (uscita) commuta solo in corrispondenza del <u>fronte di salita</u> o di <u>discesa</u> del clock.

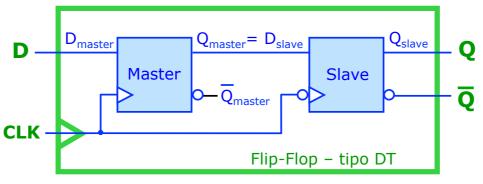

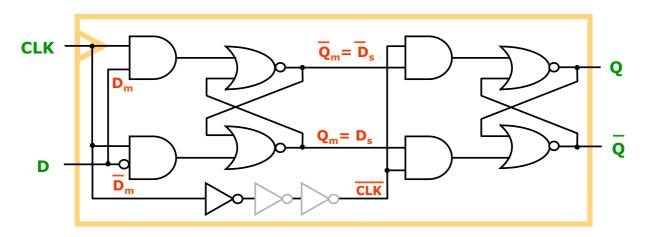

# Flip-Flop tipo DT configurazione "Master-Slave":

A.A. 2017/18 © F. Pedersini – DI, UniMI L8 – 25

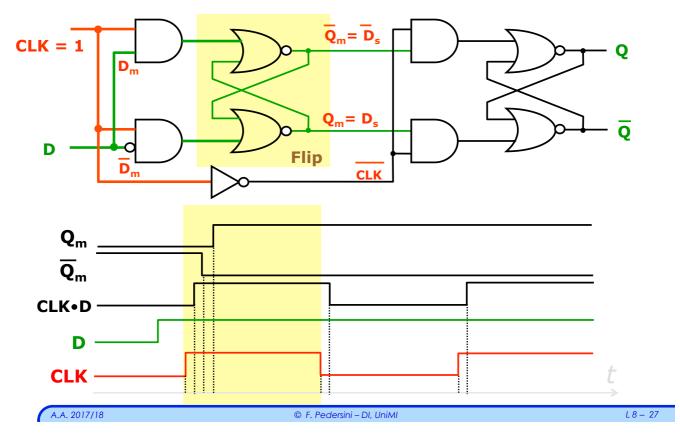

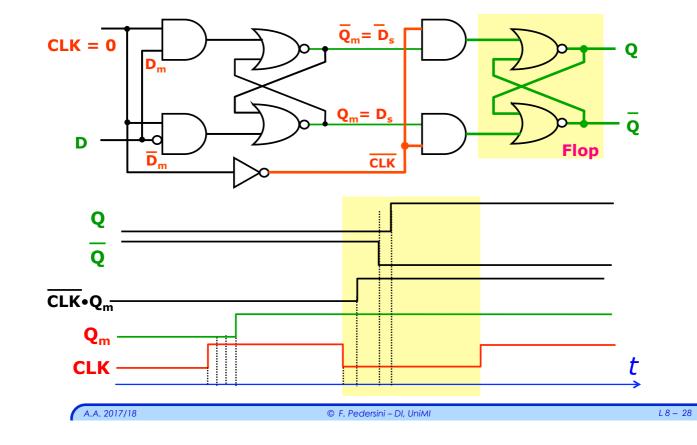

# Flip-flop: struttura master-slave

"FLIP" (clock ALTO): aperto lo stadio MASTER, chiuso lo stadio SLAVEUscita Q bloccata su un valore precedentemente memorizzato

"FLOP" (clock BASSO): chiuso lo stadio MASTER, aperto lo stadio SLAVE

Ingresso "chiuso", uscita bloccata sul valore contenuto in MASTER

# Funzionamento: FLIP

# Funzionamento: FLOP

# Funzionamento dei Flip-Flop

## Latch: Bistabili level-sensitive

I latch sono dispositivi **trasparenti:** per tutto il tempo in cui il clock è a livello alto, il valore di D viene riportato in uscita

Clock = 1 → Q\*=D (uscita collegata all'ingresso)

Possono funzionare come "cancelli"?

Nel momento in cui "apro" (T=1), i segnali possono attraversare **TUTTI gli stadi**.

Soluzione: "cancello doppio"

Quando apro in ingresso, l'uscita è chiusa, e viceversa.

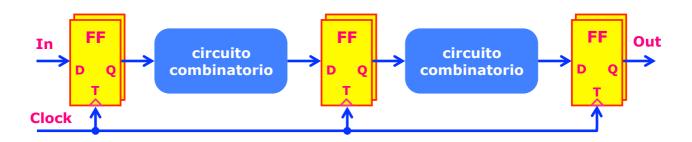

# Sincronizzazione mediante flip-flop

- I "cancelli" devono disaccoppiare i diversi sottosistemi logici

- > "memorizzare" i segnali e "rilanciarli", tutto ad un determinato istante

- > prima e dopo, uscite non sensibili agli ingressi

- > Cancello doppio: ingresso e uscita, mai aperti contemporaneamente

Cancelli:

registri costituiti da gruppi di flip-flop

A.A. 2017/18 © F. Pedersini – DI, UniMI L8 – 31

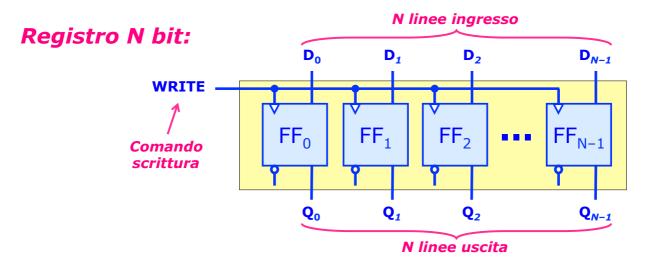

# Registri

Registro: unità di memorizzazione di parole di N bit

Struttura: N Flip-flop tipo DT

Operazioni: LETTURA: I dati memorizzati sono sempre leggibili sulle uscite Q.

SCRITTURA: un fronte di salita (o discesa) su WRITE memorizza

i valori presenti sugli ingressi D

# Architettura degli Elaboratori e delle Reti

# Circuiti sequenziali: macchine a stati finiti

Proff. A. Borghese, F. Pedersini

Dipartimento di Scienze dell'Informazione Università degli Studi di Milano

A.A. 2017/18 © F. Pedersini – DI, UniMI L 8 – 33

# Macchine sequenziali

- \* Macchina combinatoria:  $\mathbf{U} = f(\mathbf{I})$

- > senza memoria, uscita dipende solo dagli ingressi

- Macchina sequenziale:

$$\mathbf{X}^* = f(\mathbf{X}, \mathbf{I})$$

$\mathbf{U} = g(\mathbf{X})$

- > 2 funzioni: uscita e stato prossimo

- > esiste la memoria: lo STATO

## Macchina a Stati Finiti - di Moore

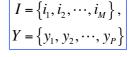

Una Macchina a Stati Finiti (FSM) è definita dalla quintupla:

#### 3 insiemi e 2 funzioni logiche:

X:insieme degli stati (in numero finito).

**I**: alfabeto di ingresso: l'insieme dei simboli che si possono presentare in ingresso. Con **n** ingressi, avremo **2**<sup>n</sup> possibili configurazioni.

**Y**: alfabeto di uscita: l'insieme dei simboli che si possono generare in uscita. Con **m** uscite, avremo **2**<sup>m</sup> possibili configurazioni

$f(\cdot)$ : funzione stato prossimo:  $X^* = f(X, I)$ Definisce l'evoluzione della macchina nel tempo, in modo deterministico

$g(\cdot)$ : funzione di uscita: Y = g(X) (macchina di Moore) Y = g(X, I) (macchina di Mealy)

Per il buon funzionamento della macchina è previsto talvolta anche uno stato iniziale, nel quale si trova la FSM all'accensione o dopo un comando di RESET

A.A. 2017/18 © F. Pedersini – DI, UniMI L 8 – 35

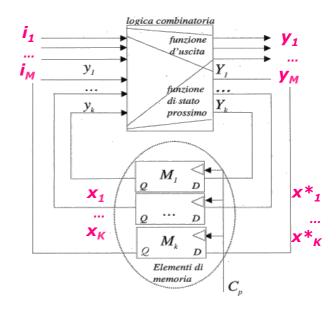

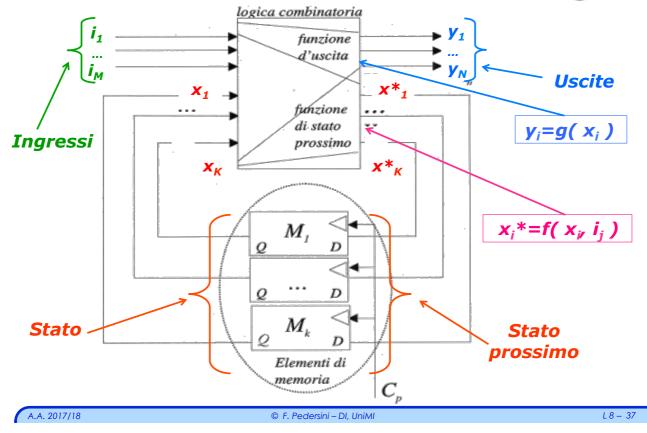

## La macchina sequenziale di Huffman

## Macchina sequenziale di Huffman

è la realizzazione pratica di una **FSM** mediante **elettronica digitale**

- Codifica BINARIA di: ingressi, uscite e stati

- Le funzioni: stato prossimo f\*=f(X,I) e uscita y=g(X) sono funzioni logiche.

## La macchina sequenziale di Huffman

# Macchina di Moore: State Transition Table (STT)

#### STT: State Transition Table (Tabella delle tran

(Tabella delle transizioni di stato)

- Per ogni coppia: <stato attuale, ingresso> definisco stato prossimo x\*

- Per ogni stato attuale, definisco l'uscita y

$$(x_i \in X, i_i \in I) \rightarrow y=g(x_i); x^*=f(x_i, i_i)$$

Esempio: macchina di Moore →

▶ **M** stati (log<sub>2</sub>M bit di stato), **N** ingressi (log<sub>2</sub>M bit d'ingresso):

|                       | i <sub>1</sub>                      | i <sub>2</sub>                      | <br>i <sub>N</sub>                  | Y                  |

|-----------------------|-------------------------------------|-------------------------------------|-------------------------------------|--------------------|

| $x_1$                 | $x^*(x_{1,i_1})$                    | $x^*(x_{1,i_2})$                    | $x*(x_{1,i_N})$                     | $y(x_1)$           |

| <b>X</b> <sub>2</sub> | $x^*(x_{2,i_1})$                    | x*(x <sub>2</sub> ,i <sub>2</sub> ) | x*(x <sub>2,</sub> i <sub>N</sub> ) | y(x <sub>2</sub> ) |

|                       |                                     |                                     |                                     |                    |

| X <sub>M</sub>        | x*(x <sub>M</sub> ,i <sub>1</sub> ) | x*(x <sub>M</sub> ,i <sub>2</sub> ) | x*(x <sub>M</sub> ,i <sub>N</sub> ) | y(x <sub>M</sub> ) |

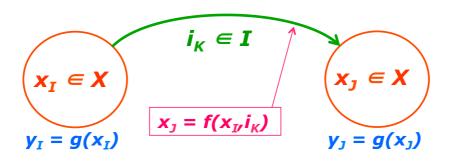

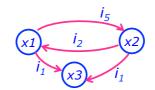

# Macchina di Moore: State Transition Graph (STG)

#### STG: State Transition Graph

(Diagramma degli Stati o Grafo delle transizioni)

- ➤ Ad ogni nodo è associato uno stato: x<sub>i</sub> ∈ X

- ... ed un valore della funzione d'uscita:  $y_i \in Y$ ,  $y_i = g(x_i)$

- > Un arco orientato da uno stato  $\mathbf{x_i}$  ad uno stato  $\mathbf{x_j}$ , contrassegnato da un simbolo (di ingresso)  $\mathbf{i_K}$ , rappresenta una transizione che si verifica quando la macchina, essendo nello stato  $\mathbf{x_i}$ , riceve come ingresso  $\mathbf{i_K}$

A.A. 2017/18 © F. Pedersini – DI, UniMI L 8 – 39

## Sintesi circuito sequenziale

#### Sequenza operazioni di sintesi

di un circuito seguenziale mediante modello a FSM:

- 1. Definizione insiemi ingressi I e uscite Y

- 2. Costruzione grafo delle transizioni STG

- $\rightarrow$  definizione insieme  $X \rightarrow f(X,I)$  e g(X)

- 3. Traduzione STG → STT

$$X = \left\{x_1, x_2, \dots, x_Q\right\}$$

|                       | i <sub>1</sub>                      | <br>i <sub>N</sub> | Y                  |

|-----------------------|-------------------------------------|--------------------|--------------------|

| <b>X</b> <sub>1</sub> | $x*(x_{1,i_1})$                     | $x*(x_1,i_N)$      | y(x <sub>1</sub> ) |

| <b>x</b> <sub>2</sub> | x*(x <sub>2</sub> ,i <sub>1</sub> ) | $x*(x_2,i_N)$      | y(x <sub>2</sub> ) |

|                       |                                     |                    |                    |

| Υ                     | x*(x i.)                            | x*(x., i.,)        | v(x)               |

- 4. Codifica binaria degli elementi di X, Y, I nella STT

- → gli elementi di I, Y e X diventano parole binarie

- $\rightarrow$  f(X,I) e g(X) diventano funzioni logiche!

- 5. Sintesi delle funzioni logiche  $f_i(X,I)$  e  $g_i(X)$

- → circuito finale con struttura di Huffman

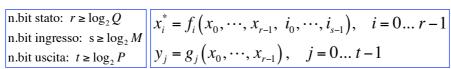

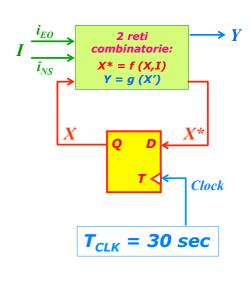

## Progetto con macchina di Moore

auto NS

auto EO

#### Esempio di SINTESI di FSM: controllore di un semaforo

#### **SEMAFORO:**

- Incrocio tra 2 strade: nord-sud (NS) ed est-ovest (EO) controllate da un semaforo

- > per semplicità consideriamo solamente rosso e verde

- Il semaforo può commutare ogni 30 secondi

- Macchina sincrona, clock con frequenza = ?

- E' presente un sensore in grado di "leggere", per ogni direttrice, se esiste almeno un'auto in attesa, oppure un'auto che si accinga ad attraversare (condizioni trattate allo stesso modo).

- Il semaforo deve cambiare colore, da rosso a verde, quando esiste un'auto in attesa sulla sua direttrice.

- Se ci sono auto in attesa sulle entrambe le direttrici il semaforo deve cambiare colore (al termine del tempo di commutazione)

A.A. 2017/18 © F. Pedersini – DI, UniMI L8 – 41

# SEMAFORO: Stato, Ingresso, Uscita

#### **INGRESSI**

- Auto NS presente / non presente

- + **AutoNS=1/0**

- > Auto EO presente / non presente

- + AutoEO = 1/0

- → 2 bit di INGRESSO → 4 configurazioni d'ingresso:  $I = \{00, 01, 10, 11\}$

- LuceEO verde (LuceNS rossa)

- LuceNS verde (LuceEO rossa)

- → 2 configurazioni d'uscita → 1 bit di USCITA

#### **STATO**

- > Semaforo NS VERDE, semaforo EO ROSSO

- > Semaforo NS ROSSO, semaforo EO VERDE

X = { "VerdeNS", "VerdeEO" }

→ 1 bit di STATO (1 flip-flop)

## Funzionamento: uscita

#### Funzione uscita

- Funzione uscita: Y = g(X)

- > Per ogni stato, definire l'uscita della macchina

- ❖ Uscita ↔ STATO → Y = X

- > VerdeNS → Verde sulla direttrice NS, rosso sulla direttrice EO

- > VerdeEO → Verde sulla direttrice EO, rosso sulla direttrice NS

- Luce Verde NS / Rosso EO = VerdeNS

- Luce Verde EO / Rosso NS = VerdeEO

A.A. 2017/18

© F. Pedersini – DI, UniMi

L8 - 43

## Funzionamento: stato prossimo

## Funzione stato prossimo

Stato prossimo: evoluzione dello stato, in funzione dello stato attuale e degli ingressi attuali

$$X(t+1) = X^* = f(X(t), I)$$

- \* X<sub>i+1</sub> = X<sub>i</sub>\* = "VerdeNS"

- > Se X(t)="VerdeNS" AND non\_ci sono auto sulla direttrice EO

- > Se X(t)="VerdeEO" AND ci sono auto sulla direttrice NS

VerdeNS · ~autoEO + VerdeEO · autoNS → X\* = VerdeNS

- **X**<sub>i+1</sub> = **X**<sub>i</sub>\* = "VerdeEO"

- ➤ Se X(t)="VerdeEO" AND <u>non</u> ci sono auto sulla direttrice NS

- ➤ Se X(t)="VerdeNS" AND ci sono auto sulla direttrice EO

VerdeEO · ~autoNS + VerdeNS · autoEO → X\* = VerdeEO

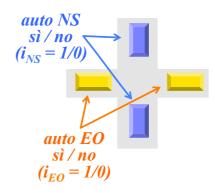

## STG del semaforo

## **Sintesi State Transition Graph (STG):**

#### Risultato:

Funzione stato prossimo:

VerdeNS\* = VerdeNS · ~autoEO + VerdeEO · autoNS VerdeEO\* = VerdeEO · ~autoNS + VerdeNS · autoEO

© F. Pedersini – DI, UniMI

Funzione uscita: Y = X

A.A. 2017/18

L8 – 45

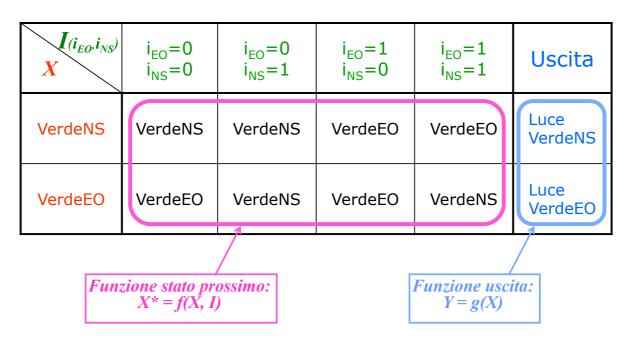

# STT del semaforo

## **Sintesi State Transition Table (STT):**

A.A. 2017/18

© F. Pedersini – DI, UniMI

L8 – 46

## STT del semaforo: CODIFICA binaria

#### Codifica binaria della STT:

#### Stato:

(VerdeNS/RossoEO, RossoNS/VerdeEO)

#### **Ingresso:**

- > 2 Variabili: (AutoEO, AutoNS) → 1 ="presente", 0 ="assente"

- $\gt$  4 Configurazioni: **I** = ( $i_{EO}$ ,  $i_{NS}$ ) = {00, 01, 10, 11}

#### **Uscita:**

> (Luce\_VerdeNS, Luce\_VerdeEO) → Y = {0, 1}

| X (i <sub>EO</sub> , i <sub>NS</sub> ) | 00 | 01 | 10 | 11 | Uscita<br><b>Y</b> |

|----------------------------------------|----|----|----|----|--------------------|

| 0                                      | 0  | 0  | 1  | 1  | 0                  |

| 1                                      | 1  | 0  | 1  | 0  | 1                  |

A.A. 2017/18 © F. Pedersini – DI, UniMI L 8 – 47

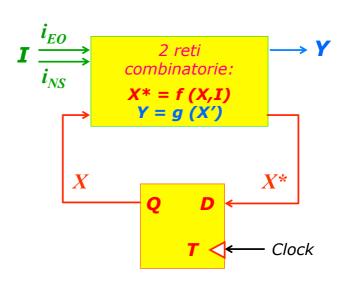

# Sintesi della MSF del semaforo

### Sintesi del circuito:

- > 2 stati  $(0,1) \rightarrow 1$  flip-flop DT

- > 2 linee di ingresso

- > 1 linea d'uscita

### Architettura di Huffman:

- Rete combinatoria che implementa:

- > stato prossimo: f(X,I)

- uscita: g(X)

# Sintesi della MSF del semaforo

- Mediante la STT codificata in binario, posso esprimere X\* e Y come somma di prodotti:

- > cerco i mintermini:

$$\begin{split} X^* &= \overline{X} \ i_{EO} \, \overline{i_{NS}} + \overline{X} \ i_{EO} \ i_{NS} + X \ i_{EO} \ \overline{i_{NS}} + X \ \overline{i_{EO}} \ \overline{i_{NS}} = \\ &= \overline{X} \ i_{EO} + X \ \overline{i_{NS}} \end{split}$$

$$Y = X$$

| $I_{(i_{EO},i_{NS})}$ | 00 | 01 | 11 | 10 | Y |

|-----------------------|----|----|----|----|---|

| 0                     | 0  | 0  | 1  | 1  | 0 |

| 1                     | 1  | 0  | 0  | 1  | 1 |

A.A. 2017/18

© F. Pedersini – DI, UniMI

L8 – 49

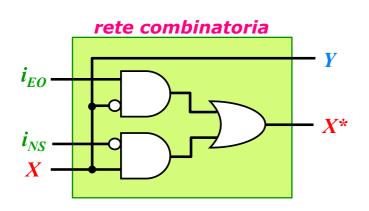

## MSF del semaforo: sintesi del circuito

funzioni logiche rete combinatoria:

$$X^* = \overline{X} \ i_{EO} \overline{i_{NS}} + \overline{X} \ i_{EO} \ i_{NS} + X \ i_{EO} \ \overline{i_{NS}} + X \ \overline{i_{EO}} \ \overline{i_{NS}} =$$

$$= \overline{X} \ i_{EO} + X \ \overline{i_{NS}}$$

$$Y = X$$

A.A. 2017/18

© F. Pedersini – DI, UniMI

L8 - 50

# Esercizi: sintesi di circuiti sequenziali

- Si progetti una macchina a stati finiti (di Moore) caratterizzata da una linea d'ingresso che viene letta ogni secondo e da un'uscita che vale "1" solo quando in ingresso si sia presentata la sequenza: "001". Si determinino: STG, STT, STT codificata e il circuito completo.

- Si progetti un contatore binario modulo 4 che presenta, su due linee d'uscita, il valore binario di conteggio (0 → 1 → 2 → 3 → 0 ...).

Il contatore viene incrementato ogni qualvolta sulla linea d'ingresso I si presenta un fronte di salita. Si suppongano inizialmente sia l'ingresso che le uscite a '0'. Si determinino: STG, STT, STT codificata e il circuito completo.

- Si sintetizzi una macchina a stati finiti di Moore caratterizzata da una linea d'ingresso IN e due linee di uscita Y<sub>0</sub> e Y<sub>1</sub>. La macchina si comporta così: ogni volta che all'ingresso IN si presenta la sequenza "011", l'uscita Y <u>cambia valore</u> mentre l'uscita Z, normalmente a '0', <u>si porta a '1' per un ciclo di clock e poi torna a '0'</u>. Si suppongano inizialmente ingressi e uscite tutti a 0. Si determinino: STG, STT, STT codificata e struttura circuitale del sistema completo, avendo cura di semplificare il più possibile le funzioni prima di tradurle in circuito.