# Architetture degli Elaboratori - I

#### Docenti:

Alberto Borghese, Federico Pedersini Dipartimento di Informatica Università degli Studi di Milano

Turno 2 (Cognomi G–Z) Prof. Federico PEDERSINI pedersini@di.unimi.it

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

# Architetture Elaboratori I–II (6+6 CFU)

#### **Orario lezione:**

martedì 10.30-12.30 Aula G13

giovedì 10.30-12.30 Aula G13

#### **Laboratorio** (a partire dalla prossima settimana):

Turno A: cognomi **A-F** giovedì 13.30-15.30 – **Aula 307** (Nicola BASILICO) Turno B: cognomi **G-Z** giovedì 13.30-15.30 – **Aula 309** (Matteo RE)

Inizio Laboratorio: 5 ottobre

#### Orario di ricevimento:

durante il corso: al <u>termine</u> di ogni lezione

resto dell'anno: su appuntamento (e-mail)

#### **MATERIALE DIDATTICO**

- \* Appunti + slide

- > Slide delle lezioni: homes.di.unimi.it/~pedersin/AE-INF.html

- ➤ Le slide da sole NON BASTANO!

- \* Testi di riferimento:

In inglese:

D.A. Patterson, J.L. Hennessy,

"Computer Organization & Design: The Hardware/Software Interface",

Morgan Kaufmann, 2005.

In italiano:

- D.A. Patterson, J.L. Hennessy,

"Struttura e Progetto dei Calcolatori", Zanichelli, 2006

- \* testo di approfondimento su circuiti logici

- > M.M. Mano, C.R. Kime, "Reti Logiche", Pearson, IV ed., 2008.

- > F. Fummi, M.G. Sami, C. Silvano, "Progettazione digitale", McGraw-Hill.

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

9

#### Esame

# **MODALITÀ D'ESAME Architettura I / Architettura II**

- ESAME (prova scritta + prova orale) → voto1

- PROGETTO di laboratorio (con l'esercitatore) → voto2

Arch. I: progettazione circuitale

Arch. II: programmazione Assembly

Voto finale = round(2/3 voto1 + 1/3 voto2)

Periodo di **validità** di ESAME e PROGETTO: **12 mesi** (max. distanza cronologica tra esame e progetto)

# Obiettivi di questo insegnamento

# A COSA SERVE un corso di Architettura degli Elaboratori ad uno studente di Informatica?

Che cos'è l'Informatica?

La scienza che studia il trattamento automatico (elaborazione) delle informazioni.

Obiettivo dell'insegnamento di Architetture:

comprensione del funzionamento della macchina che tratta le informazioni in modo automatico.

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

- 4

#### PROGRAMMA

Per arrivare a tale obiettivo, seguiremo questo...

#### **PROGRAMMA**:

- 1. Rappresentazione delle informazioni con un alfabeto binario

- 2. Elaborazione di informazioni binarie: algebra di Boole, funzione logica.

- 3. Elaborazione automatica di informazioni binarie

- 3.1 rappresentazione elettrica di informazione binaria

- 3.2 costruzione di operatori logici con "macchine elettriche (dispositivi elettronici)"

- 4. Progetto di circuiti a partire dalla funzione logica

- 5. Come memorizzare informazioni binarie

- 6. Progetto di circuiti con memoria

- 7. Progetto di un elaboratore completo

# Obiettivo del corso

#### "Missione" dei corsi di Architettura 1 e 2: comprendere il funzionamento di un elaboratore elettronico

#### **LEZIONE**

#### Fondamenti di elettronica digitale

- > Algebra di Boole

- Logica combinatoria

- > Macchine sequenziali

- > La CPU

#### Il linguaggio del calcolatore

- > Programmazione Assembly

- > Linguaggio macchina

#### Come funziona un calcolatore moderno

- > CPU

- > memorie (cache)

- ➤ I/O (bus, interrupt e DMA, ...)

- > Architetture moderne (multiprocessore, multicore, GPU, ...)

#### **LABORATORIO**

#### I. Progettazione di circuiti digitali

**LOGICLY/LOGISIM**: ambienti di progettazione e simulazione di circuiti digitali

http://sourceforge.net/projects/circuit/

# **Architettura 1**

# II. Programmazione CPU in Assembly

**SPIM** (e altri): ambiente di simulazione elaboratore con CPU MIPS32

http://spimsimulator.sourceforge.net

# **Architettura 2**

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

# Storia dell'elaboratore (i primi passi)

# Storia degli elaboratori

- Applicazione originaria di un elaboratore:

calcolo automatico

- \* Babilonesi, X secolo a.C.

- > Abaco

- > Evoluzioni fino a 1000 d.C.

- \* B. Pascal, 1642

- Pascalina (somma e sottrazione)

- ❖ G. von Leibnitz, 1673

- Macchina calcolatrice (moltiplicazione e divisione)

# Storia dell'elaboratore (1800)

- Applicazioni dell'elaboratore alternative al calcolo:

CAM (Computer-Aided Manufacturing)

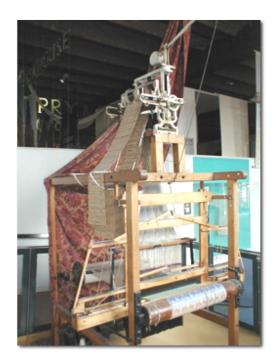

- Telaio Jaquard (1801):

prima <u>macchina programmabile</u>

della storia

- > Programma di lavoro su schede

- > Macchina dedicata

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

-

# Storia dell'elaboratore (1800)

#### Classificazione Hardware / Software

#### Hardware:

Charles Babbage (1840) padre del calcolatore moderno. Inventa:

"Analytical Engine"

- Azionata a vapore (impossibile da costruire al tempo)

- Programmabile: programmi su schede

#### Ada Lovelace (1830):

Formalizzazione del concetto di programma

# Storia dell'elaboratore (1900 – 1940)

#### 1890 - 1940: elaboratori elettromeccanici - sviluppo prestazioni

❖ 1890: H. Hollerith – Schede perforate a lettura <u>elettromeccanica</u> (relais).

1932: T.J. Watson rileva il brevetto e fonda la "International Business Machines" (IBM).

1939: ABC – Atanasoff Berry Computer (University of Iowa)

> Elettromeccanico: ampio utilizzo di elettrovalvole e relé.

> Memoria cancellabile e riscrivibile

#### → Miniaturizzazione:

Sviluppo di <u>calcolatrici da tavolo</u> meccaniche (diffusione nel commercio)

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

11

# La prima generazione (ENIAC: 1946-1955)

#### 1940 - 50: avvento dell'elettronica (a valvole)

> Aumento di prestazioni di 1000 volte

"Prima generazione" di elaboratori elettronici

- ENIAC (Electronic Numerical Integrator And Calculator) (University of Pennsylvania, 1946)

- > 20 registri da 10 cifre

- ➤ 18,000 valvole

- > 70,000 resistenze

- > 10,000 condensatori

- > 6.000 interruttori

- ➤ Dimensioni: 30 x 2.5 x 3 metri

- > Peso: 30 tonnellate

- > Consumo: 140 kW

- > 100 operazioni/s

- > Programmazione manuale

# La prima generazione (1945-1951)

- Programma memorizzato su supporto intercambiabile

- > (John Von Neumann, 1945)

- Eckbert, Mauchly

- > EDVAC (V. Neumann),

- > Mark I, 1948

- > EDSAC (Cambridge, 1949)

- UNIVAC I

(Universal Automatic

Computer),

- Eckbert, Mauchly, 1951.

- Primo calcolatore commercializzato (1 M\$)

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

- 1

## Applicazioni scientifiche vs. gestionali

### **Applicazioni scientifiche:**

- UNIVAC: calcolo scientifico (1950).

- > Calcoli lunghi e complessi

### Applicazioni gestionali:

- ❖ IBM: mod. 701 (1953) e 702 (1955): applicazioni gestionali

- > Calcoli semplici e ripetitivi

- > Grandi quantità di dati

- ❖ IBM 704 Memoria con nuclei di ferrite

- > 32,000 parole

- ➤ Velocità di commutaz. di pochi µsec (I/O rate: 1÷10 kHz)

- ❖ IBM 709 (1958) Introduzione del "canale" di I/O.

## La seconda generazione (1952 – 1963)

# **1950–60**: Introduzione **elettronica allo stato solido** e memorie a nuclei ferromagnetici.

- IBM 7000 Transistor anziché valvole

- ❖ IBM 7094 (1962) evoluzione del 709, a stato solido.

- CDC 6600 Primo supercalcolatore. 1962.

- CDC 3600 Multi-programmazione. 1963.

- Digital PDP-1 (1957)

- SOFTWARE: introduzione del FORTRAN (Formula Translator).

- > Primo linguaggio ad alto livello

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

1

### La terza generazione (1964 –1971)

# 1960: Avvento dei circuiti integrati (LSI)

- ❖ IBM 360 (1964) Prima famiglia di calcolatori

- > Costo: 360,000 \$

- > Registri a 32 bit.

- ➤ Clock 1÷4 Mhz.

- \* Digital PDP-8 (1965)

- > Primo minicalcolatore

- > Costo: **20,000** \$

- ❖ Digital PDP-11 (1970)

- diventa uno standard negli ambienti accademici

# La quarta generazione (1971-1977)

#### 1970:

- Miniaturizzazione su larga scala (VLSI)

- Introduzione del microprocessore Memorie a semiconduttore

- → Prestazioni: Super-computers

- > Cray I (1976): primo supercalcolatore Vettoriale

- ➤ Intel 4004 (1971) 4 bit

- ➤ Intel 8080 (1974) 8 bit

- ➤ Motorola 6502

- Xerox Research Labs & Steve Jobs: primo Personal Computer: Apple II (1977)

- → Processore Motorola (6502)

- + Costo medio 2,000\$

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

17

# Quarta/quinta generazione

# 1980: Computer alla portata di singolo utente

- \* **IBM**: il primo **PC** (1981)

- Sistema operativo MS-DOS (Microsoft di Bill Gates)

- > Processore Intel 8086.

- > Coprocessore Matematico Intel 8087.

- La quinta generazione (1977-....)

#### PC come Workstation

- > Potenziamento della grafica. Coprocessore grafico.

- > Multi-processori.

- > Introduzione di gerarchie di calcolo.

- > Processori RISC (Reduced Instruction Set Code).

# Sesta generazione (futuro)

#### 20...

- \* Tecnologie

- > Calcolatori ottici.

- > Calcolatori chimici.

- Co-processori specializzati per:

- > ricerca in data-base.

- > trattamento grafica.

- > trattamento video.

- Macchine "onnipresenti"

- > smartphone, auto, casa, ...

- Macchine parallele

- \* Macchine intelligenti e sensibili.

- Sistemi multimediali.

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

1

# Legge di MOORE

#### Legge di MOORE:

Ogni circa 18 mesi, le prestazioni raddoppiano

la velocità di calcolo, il numero di transistor nei chip, la capacità delle memorie.

| Anno | Nome                | Dimensoni<br>(m³) | Potenza<br>(Watt) | Prestazioni<br>(somme/sec) | Memoria<br>(kbyte) | Prezzo<br>rivalutato | Prezzo/prestazioni<br>(vs. UNIVAC) |

|------|---------------------|-------------------|-------------------|----------------------------|--------------------|----------------------|------------------------------------|

| 1951 | UNIVAC I            | 28                | 124 500           | 1 900                      | 48                 | 4 996 749            | 1                                  |

| 1964 | IBM 360 modello 50  | 1.68              | 10 000            | 500 000                    | 64                 | 4 140 257            | 318                                |

| 1965 | PDP-8               | 0.23              | 500               | 330 000                    | 4                  | 66 071               | 13 135                             |

| 1976 | Cray-1              | 1.62              | 60 000            | 166 000 000                | 32                 | 8 459 712            | 51 604                             |

| 1981 | IBM-PC              | 0.03              | 150               | 240 000                    | 256                | 4 081                | 154 673                            |

| 1991 | HP900 modello 750   | 0.06              | 500               | 50 000 000                 | 16 384             | 8 156                | 16 122 356                         |

| 1996 | Pentium Pro 200 Mhz | 0.06              | 500               | 400 000 000                | 16 384             | 4 400                | 239 078 908                        |

| 2003 | Pentium 4 3.0 GHz   | 0.06              | 500               | 6 000 000 000              | 262 144            | 1 000                | 11 452 000 000                     |

# Legge di Moore: alcuni problemi

- \* La velocità delle memorie non cresce con la velocità del processore.

- ➤ Memorie gerarchiche cache.

- > Aumento della parola di memoria.

- > high-speed bus (gerarchie di bus)

- Tecniche di velocizzazione dell'elaborazione.

- > Predizione dei salti.

- Scheduling ottimale delle istruzioni

(analisi segmenti di codice).

- > Esecuzione speculativa.

- Tecniche di velocizzazione del trasferimento dati (I/O)

- > Trasferimento diretto in memoria (DMA)

- Velocizzazione e specializzazione dei bus

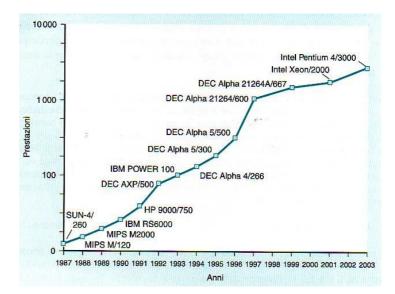

Evoluzione della potenza di calcolo (1987–2003) Patterson-Hennessy, 2006

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

21

#### Evoluzione INTEL: 1970 ÷ 1990

|                 | 4004      | 8008     | 8080     | 8086     | 8088     |

|-----------------|-----------|----------|----------|----------|----------|

| Introduced      | 15 nov 71 | 1 Apr 72 | 1 Apr 74 | 8 Jun 76 | 6 Jan 79 |

| Clock speed     | 108 kHz   | 108 kHz  | 2 Mhz    | 5-10 Mhz | 5,8 Mhz  |

| Bus width       | 4 bit     | 8 bit    | 8 bit    | 16 bit   | 8 bit    |

| No. transistors | 2,300     | 3,500    | 6,000    | 29,000   | 29,000   |

| Memory          | 640byte   | 16KByte  | 64 KByte | 1MByte   | 1MByte   |

| Virtual Memory  | -         | -        | -        | -        | -        |

|                    | 80286                | 80386 DX      | 80386 SX  | 80486 DX                |

|--------------------|----------------------|---------------|-----------|-------------------------|

| Introduced         | 1 feb 82             | 17 Oct 85     | 16 Jun 88 | 10 Apr 89               |

| Clock speed        | 6-12.5MHz            | 16-33MHz      | 16-33Mhz  | 25-50Mhz                |

| Bus width          | 16 bit               | 32 bit        | 16 bit    | 32 bit                  |

| No. transistors    | 134,000              | 275,000       | 275,000   | 1,200,000               |

| Addressable Memory | 16Mbyte              | 4GByte        | 4GByte    | 4GByte                  |

| Virtual Memory     | 1 GByte              | 64 TByte      | 64 TByte  | 64 TByte                |

| Observations       | 15 milioni in 6 anni | Multi-tasking | 64 TByte  | Co-processore nella CPU |

|                    | 80486 SX  | Pentium         | Pentium Pro     | Pentium II                 |

|--------------------|-----------|-----------------|-----------------|----------------------------|

| Introduced         | 22 Apr 91 | 22 Mar 93       | 1 Nov 95        | 7 May 97                   |

| Clock speed        | 6-133MHz  | 60-166MHz       | 150-200Mhz      | 200-300Mhz                 |

| Bus width          | 32 bit    | 32 bit          | 32/64 bit       | 32/64 bit                  |

| No. transistors    | 1,185,000 | 3,100,000       | 5,500,000       | 7,500,000                  |

| Addressable Memory | 4 Gbyte   | 4 GByte         | 64 GByte        | 64 GByte                   |

| Virtual Memory     | 64 TByte  | 64 TByte        | 64 TByte        | 64 TByte                   |

| Observations       |           | Pipeline spinto | Cache 2 livelli | MMX, memorie alta velocità |

## Evoluzione Intel – 1990 ÷ ...

|                    | Pentium III | Pentium 4          | Pentium III Xeon              |  |

|--------------------|-------------|--------------------|-------------------------------|--|

| Introduced         | 26 Feb 99   | Nov 2000           | 2001                          |  |

| Clock speed        | 450-660MHz  | 3 GHz              | 2-3.2Ghz                      |  |

| Bus width          | 32/64 bit   | 32/64 bit          | 32/64 bit                     |  |

| No. transistors    | 9,500,000   | 42,000,000         | Na                            |  |

| Addressable Memory | 64 Gbyte    | 64 GByte           | 64 GByte                      |  |

| Virtual Memory     | 64 TByte    | 64 TByte           | 64 TByte                      |  |

| Observations       | SIMD        | 2 livelli di cache | Architettura di bus: NetBurst |  |

|                    | ITANIUM       | ITANIUM 2                        | Pentium M                               | Core DUO                           |

|--------------------|---------------|----------------------------------|-----------------------------------------|------------------------------------|

| Introduced         | 2002          | 2002                             | 2003                                    |                                    |

| Clock speed        | 800 MHz       | 1.3-1.5 GHz                      | 1.3-1.7 Ghz                             | 2.5 GHz                            |

| Bus width          | 64 bit        | 64 bit                           | 64 bit                                  | 64 bit                             |

| No. transistors    | na            | na                               | 42,000,000                              | 151,000,000                        |

| Addressable Memory | 16 Gbyte      | 16 Gbyte                         | 64 GByte                                | 64 GByte                           |

| Virtual Memory     | 64 TByte      | 64 TByte                         | 64 TByte                                | 64 TByte                           |

| Observations       | EPIC – 64 bit | 6.4 GByte/s su<br>Bus di sistema | Centrino Architecture<br>Very-low power | 2 cores x86-64,<br>Cache in comune |

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

2

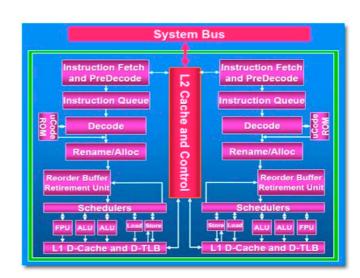

# Esempio: INTEL Core Duo

# Cambio di rotta: efficienza energetica

#### Intel Core Duo (2006)

(product code: 80539 - "Yonah")

- > 2 cores identici (Pentium III) sullo stesso "die"

- 2 Mbytes di cache L2 condivisi

- arbitraggio per l' accesso alla cache L2 e al FSB.

- Hardware di controllo CPU per la riduzione del consumo energetico

# Sviluppi futuri delle architetture

#### Dopo il 2003, evoluzione in altre direzioni:

#### Efficienza (istruzioni/s / Watt)

> INTEL Pentium M / Centrino

#### Ottimizzazione rapporto uomo/macchina

> INTEL Core DUO

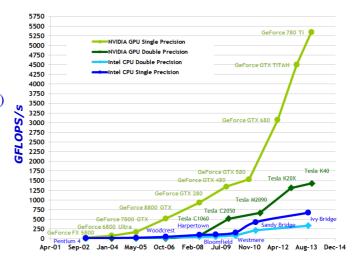

# Parallelizzazione di architetture semplici: architetture MANY-CORE

- > STI CELL processor (Playstation III)

- > GPU (Nvidia CUDA architecture)

A.A. 2017/18

© F. Pedersini – Dip. Informatica, Università degli studi di Milano

25