## Architettura degli Elaboratori e delle Reti

Turno 2 - Prof. Federico PEDERSINI

Università degli Studi di Milano Dip. Scienze dell' Informazione

Appello del: 14 febbraio 2006

Cognome, nome: Matricola:

- 1. [6] Si consideri una cache a mappatura diretta di capacità <u>C = 32 kByte</u> e con linee contenenti <u>8 parole</u>, utilizzata da una CPU caratterizzata da un bus indirizzi di 24 bit e bus dati di 16 bit.

- Dimensionare e disegnare lo schema della cache, mettendo in evidenza come le diverse parti dell'indirizzo di memoria centrale controllino il circuito.

- Indicare in che posizione viene scritto il byte all'indirizzo 0xFA8420.

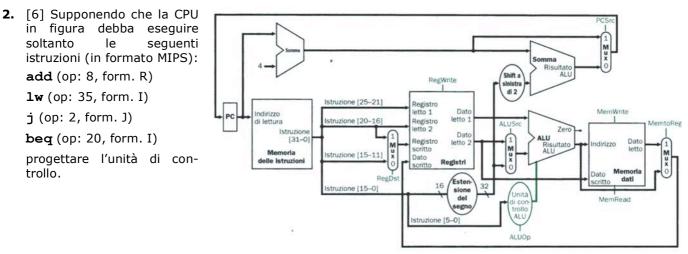

- in figura debba eseguire soltanto le sequenti istruzioni (in formato MIPS): **add** (op: 8, form. R) **1w** (op: 35, form. I) j (op: 2, form. J) **beq** (op: 20, form. I) progettare l'unità di controllo.

- 3. [7] Si sintetizzi una macchina a stati finiti di Moore (rappresentando STG, STT e struttura circuitale) che riceve in ingresso sequenze di bit e presenta due linee d'uscita, U1 ed U2. La linea U1 assume il valore '1' soltanto se sia stata ricevuta la sequenza '000', mentre U2 va a '1' solo quando si riceve la sequenza '1111'. Lo stato iniziale della macchina sia quello di sequenza vuota.

- **4.** [7] Si traduca in linguaggio Assembly il seguente frammento di codice. (N.B. Si trattino opportunamente le procedure-foglia e –non-foglia. Nel prodotto, si consideri la parola meno significativa. Nei commenti, si specifichi la corrispondenza tra le variabili C e Assembly)

```

int sommaquad( unsigned int  n )

unsigned int s;

if(n == 0)

s = 0;

s = quad(n) + sommaquad(n-1);

else

return(s);

int quad( unsigned int  v )

unsigned int vq = v*v;

return ( vq );

```

- 5. [4] Descrivere, mediante il suo diagramma di flusso, l'algoritmo di moltiplicazione "firmware" e disegnarne la corrispondente struttura circuitale.

- 6. [2] Un calcolatore viene dotato di un coprocessore matematico in grado di effettuare operazioni in virgola mobile con una velocità 9 volte superiore. Calcolare quanto deve essere la percentuale di tempo dedicata ad operazioni in virgola mobile, per la quale la velocità globale del sistema risulta raddoppiata.

- 7. [2] Descrivere le strutture necessarie in una CPU per la gestione di interrupts e le principali strategie di gestione della risposta allo stesso.

- 8. [2] Quando e perché è necessario un arbitraggio nella gestione di un bus? Descrivere le più comuni tecniche di arbitraggio utilizzate nei bus dei calcolatori.