## **Architettura degli Elaboratori e delle Reti** Turno 2 – Prof. Federico PEDERSINI

## II Compitino in itinere - 8 giugno 2004

## Università degli Studi di Milano Dip. Scienze dell'Informazione

Nome: Matricola:

- 1. Cosa rappresentano l'altezza e l'ampiezza di una memoria? Quanti bit sono necessari per indirizzare una memoria di capacità C [2]?

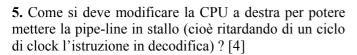

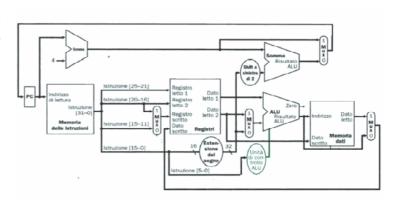

- **2.** Quali sono le modifiche che si devono operare all'architettura a fianco per farla diventare una CPU multi-ciclo? E per farla diventare una architettura con Pipe-line? [3+3]

- **3.** Quali sono i possibili meccanismi di aggiornamento del PC di una CPU? [3]

- **4.** Con riferimento alla CPU riportata qui a fianco, specificare il contenuto dei registri ed il valore dei segnali di controllo al termine (prima della commutazione del clock) del terzo stadio di esecuzione dell'istruzione **1w**: [8]

400: add \$t0, \$t1, \$t2 404: addi \$t1, \$t2, 100 **408:** lw \$t4, 0(\$t1) 412: beq \$t5, \$t6, -8 416: add \$t0, \$t1, \$t2

- **6.** Cosa si intende per *pipeline super-scalare*, pipeline a *schedulazione dinamica* e per *super-pipeline*? Quale di queste definizioni si ritrova nell'architettura del Pentium IV? [2]

- 7. Rappresentare graficamente la struttura delle seguenti tre cache:

- a) Cache a mappatura diretta con capacità di 64 byte e linee contenenti 2 parole di 4 byte.

- b) Cache a 2 vie (2-associativa) di 64 byte con linee contenenti 2 parole di 4 byte.

- c) Cache completamente associativa di 64 byte, con linee contenenti 2 parole di 4 byte.

Data l'istruzione: lw \$t0, 256(\$t1), specificare all'interno delle cache a), b), c) dove si trova la parola che deve essere letta (si scelga a piacere il valore contenuto nel registro t1). [6]

- **8.** Definire le codifiche "Manchester Encoding" e "4B/5B", specificando in cosa si differenziano. Specificare inoltre gli standard in cui vengono applicati e a che livello ISO/OSI ci troviamo. [3]

- **9.** Cosa si intende per *maschera di interrupt* e a cosa serve? [2]

- **10.** Supponiamo che una cache sia 5 volte più veloce della memoria principale ed inoltre che la cache possa venire usata per il 90% del tempo. Qual'è il guadagno in velocità dovuto all'uso della cache? Quanto sarebbe invece il guadagno se le cache fossero due, una 5 volte e l'altra 10 volte più veloce, e venissero utilizzate in modo alternato? [2+2]

- 11. Su quali principi sono basate le SRAM e le DRAM? [2]

- **12.** Quali sono le differenze principali fra le architetture IA-32 e MIPS? Qual'è l'utilizzo preferenziale di almeno 4 dei registri di un'architettura IA-32? [2]

Gli esercizi 4, 5 e 7 sono obbligatori.